# COMMITTED TO INNOVATION, CEA-Leti CREATES DIFFERENTIATING SOLUTIONS WITH ITS PARTNERS

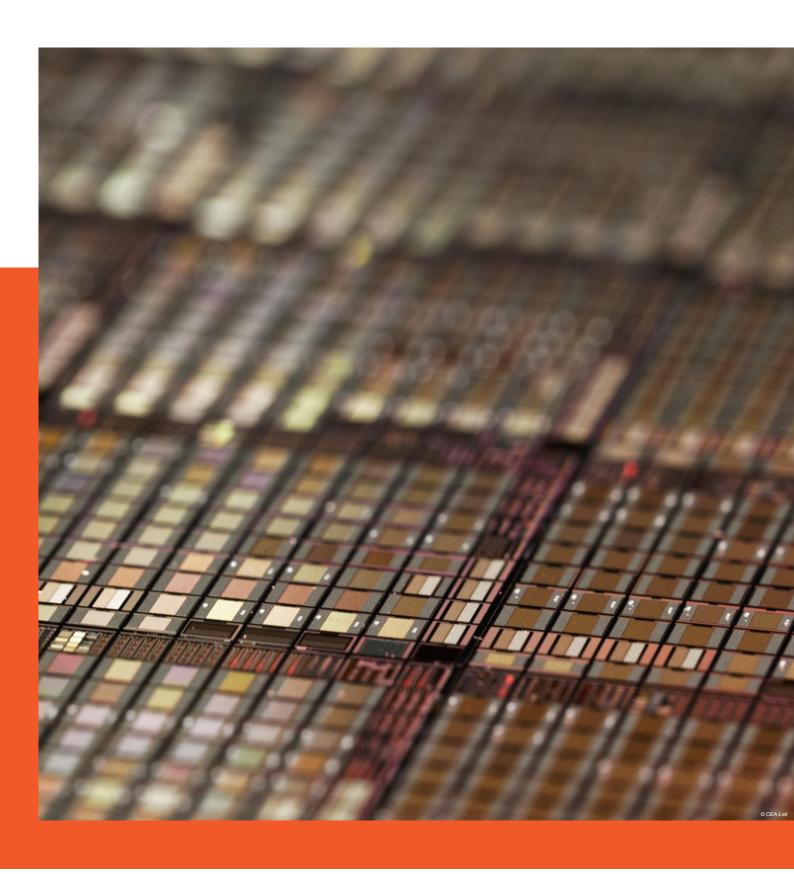

EA-Leti is a technology research institute of France's CEA and a global leader in miniaturization technologies enabling smart, energy-efficient, and secure solutions for industry. Founded in 1967, CEA-Leti conducts pioneering micro and nanotechnology research and custom develops differentiating application-specific solutions for global companies, SMEs, and startups. CEA-Leti

tackles critical challenges in healthcare, energy, and digital migration. From sensors to data processing and computing solutions, CEA-Leti's multidisciplinary teams deliver solid expertise, leveraging world-class pilot production lines to scale new technologies up. With a staff of more than

1,900, a portfolio of 3,140 patents, 10,000 sq. meters cleanrooms, and a rigorous IP policy, CEA-Leti has launched 69 startups and is a member of France's Carnot research network. based in Grenoble, France, the institute has offices in Silicon Valley and Tokyo.

Follow us at www.leti-cea.com and @CEA Leti.

#### **Technological expertise**

CEA (the French Alternative Energies and Atomic Energy Commission) is a leading global research organization whose mission is to transfer new scientific knowledge and innovations to industry. With a focus on electronics and integrated systems from micro to nano, CEA innovations make businesses in transportation, health, safety, and telecommunications more competitive by helping them develop high-performance, differentiating products and novel solutions.

www.cea.fr/english

# **CEA-Leti** at a glance

450

publications per year

ISO 9001 certified since 2000

114 European projects Founded in

1967

Based in

France (Grenoble) with offices in the

US (San Francisco) and Japan (Tokyo)

300 industrial partners

1,904 researchers

3,140 patents in portfolio

10,000

sq. meters of cleanrooms 100-200-300 mm wafers

69

startups created

Within CEA Tech and Leti, silicon technologies and components research activities are shared between two divisions gathering together around 600 researchers:

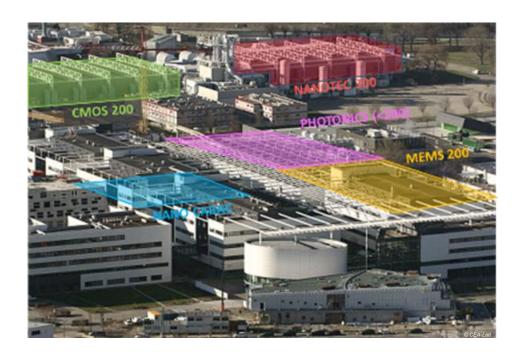

The Technology Platform Division carries out innovative process engineering, materials research and development as well as advanced nano-characterization. It operates 24/6 year round, and has  $1100 \, \text{m}^2$  of state-of-the-art cleanroom space divided into four different technology platforms.

The Silicon Components Division carries out research on nanoelectronics and heterogeneous integration on silicon and is focusing on two mains areas: on-going shrinking of CMOS devices to extend Moore's Law for faster, less-expensive computing power, and the integration of new capabilities into CMOS, such as sensors, power devices, imaging technology, and new types of memory, to enable new applications.

This booklet contains 46 one-page research summaries covering advances in the focus areas of our Silicon Devices and Technologies Divisions, highlighting new results obtained during the year 2020.

## **Technological Platforms**

The silicon divisions operate 11000 m² of state-of-the-art cleanroom space divided into three platforms, gathering 700 process tools and a combined staff of more than 520; they run industry-like operations, 24 hours a day, 6 days a week, all year round.

- 1 The Nanotech200&300 platform provides 200mm and 300mm CMOS wafer processing, which can be applied to both semiconductor and microsystem devices.

- 2 The MEMS200 platform produces non-CMOS Micro-ElectroMechanical Systems (MEMS)

- Both platforms are focused on the More than Moore initiative to develop new semiconductor capabilities. An innovative cleanroom shuttle system links the two platforms to add process flexibility and faster processing.

- 3 The 3D Integration platform aims to integrate various microelectronics objects together in order to juxtapose complementary functions, such as sensing, storing, processing, actuation, communication and energy scavenging. This provides advanced system solutions in three dimensions. This line is open to our customers for prototyping through the Open3D service.

- 4 The fourth platform that was recently added is dedicated to photonics. It covers conception, III-V and II-VI semiconductor technology fabrication and packaging capability. Applications as diverse as lighting, micro-screens, visible and infrared detectors and devices for astrophysics ...

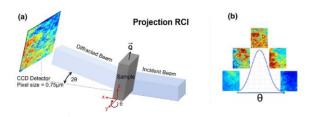

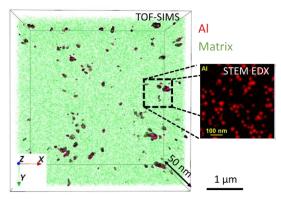

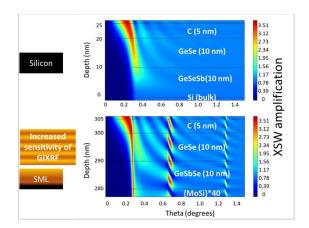

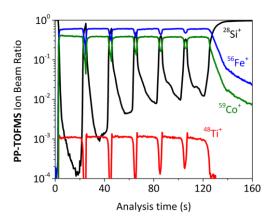

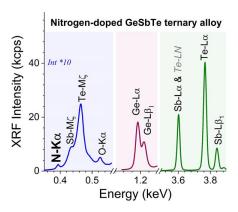

All research carried out in our cleanrooms benefits from the Nano-Characterization Platform, which is located on the MINATEC campus. This platform, unique in Europe, covers eight domains of competencies, including electron microscopy, X-ray diffraction, ion beam analysis, optics, scanning probe, surface analysis and sample preparation, magnetic resonance.

# CONTENTS

| FOREWORD                                  | 8  |

|-------------------------------------------|----|

| KEY FIGURES                               | 14 |

| SCIENTIFIC ACTIVITY                       | 16 |

| 01 / Core & Beyond CMOS                   | 18 |

| 02 / Memories                             | 24 |

| 03 / Patterning                           | 34 |

| 04 / MEMS, NEMS & RF components           | 42 |

| 05 / Power & Energy                       | 48 |

| 06 / Emerging processes and devices       | 56 |

| 07 / 3D integration & packaging           | 66 |

| 08 / Materials & technology for photonics | 72 |

| 09 / Characterization                     | 78 |

| 10 / PHD Degrees awarded in 2020          | 86 |

# **FOREWORD**

Laurent Clavelier,

Head of the Technology

Platform Division

Although the year 2020 will certainly be remembered for the sanitary crisis, it was above all the year in which we had to adapt to a unique new context.

The scientific activity of the Technology Platform Division was inevitably impacted by the constraints imposed by the pandemic and our capacity to adapt was one of our best assets in maintaining our scientific excellence.

The confinement, for example, was the opportunity to boost our scientific output both in terms of quantity with 125 scientific articles in 2020 compared to 90-100 on average whilst maintaining the number of conference proceedings constant compared to previous years, but also in quality with an improvement in our average impact factor (3.9 vs 3.5 in 2019).

Of course, these good results should not mask the difficulties encountered, especially those experienced by our PhD students, the majority of whom had their contracts extended from 2 to 4 months to take into account the period during which they were unable to access the CEA laboratories.

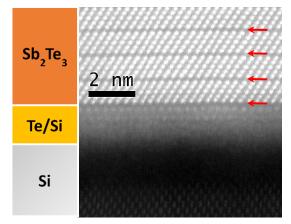

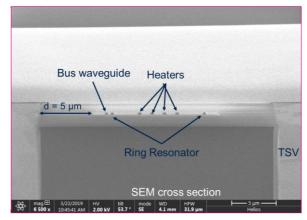

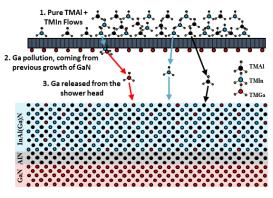

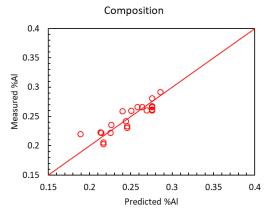

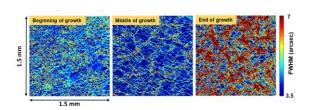

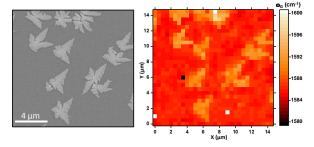

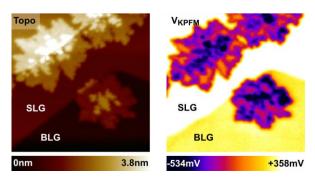

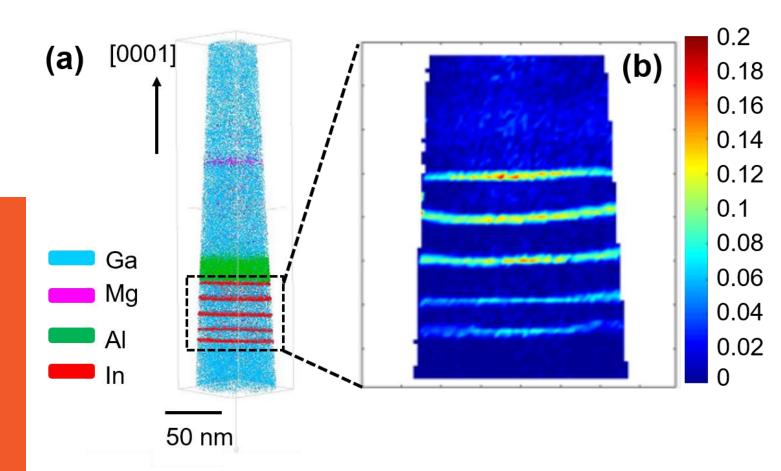

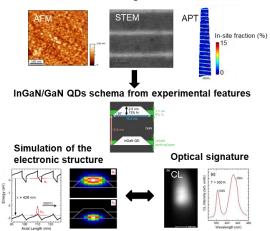

Without trying to be exhaustive, this editorial is also the opportunity to highlight some of the excellent results obtained in 2020 such as those in the domain of resistive memories based on chalcogenides and hafnium oxide that underline our position as a world leader in the domain of embedded artificial intelligence, our work on the growth of III-N materials and their advanced characterization (correlation of atom probe tomography, TEM; CL/PL), or the recent progress in 3D technology where innovative low temperature growth processes have been developed for sequential 3D applications and film transfer techniques compatible with 5  $\mu m$  interconnect pitch for 3D stacking technology.

The last point that I wish to address in this editorial is the link between research and engineering activities on the platform. Since late 2019 we have held regular meetings to ensure a strong link between these two activities to ensure that our scientific research feeds into our engineering "tool box", benefiting our industrial partners, and thus fulfilling our mission statement "from research to industry". For example, since 2020, certain aspects of our research on 2D materials found an application with STMicroelectronics for RF components. This is one of many illustrations of the continuum – research – engineering – maturation and industrial transfer that is our raison d'être

I hope you will enjoy reading the 2020 Silicon Technologies and Components scientific report.

Laurent CLAVELIER

# **FOREWORD**

Olivier Faynot, Head of Silicon Components Division

Dear Reader,

The developments of energy efficient silicon technologies and solutions is the priority of the Silicon Components Division, in order to provide answers to many societal issues such as mobility, communications with Smart, green, efficient transportations, secure and energy efficient communications. The coupling of technology, simulation, characterization, modeling, design environment and circuit design is essential to understand the behavior and to highlight the benefit of our solutions.

In spite of the 2020 COVID crisis, many significant achievements have been demonstrated this year and we have published more than 160 papers, with significant contributions to the most relevant conferences. Let me now highlight a few of our main successful achievements:

- Multilevel resistive-RAM cells have been demonstrated for Neuromorphic applications. This opens the way for denser and more efficient Neural networks.

- Silicon based quantum devices have been demonstrated and the flow has been transferred into a more robust flow using immersion lithography. Wafers are about to be finished and electrical tests will be done soon.

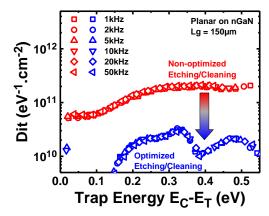

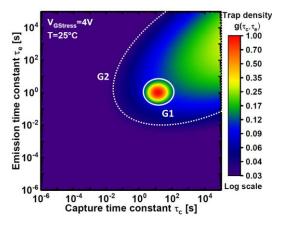

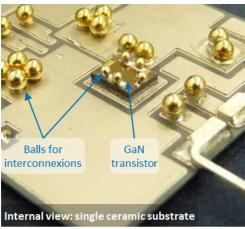

- First RF characterizations of GaN/Si transistors with optimized epitaxial layer have been performed and the first results are encouraging.

- First demonstration of SAW filters integrated on 200mm POI wafers, with similar results compared to 100 and 150mm wafers.

I would like to thank all the teams involved in those achievements and I hope you will enjoy reading the overview.

# **FOREWORD**

Jean-Charles Barbé and Jean-Paul Barnes Chief Scientists for the Silicon Components Division and the Technology Platforms Division

We are delighted to share with you our eleventh Silicon Technologies and Components Annual Scientific Research Report. This report contains 46 one-page research highlights from the Silicon Components and Technology Platforms Divisions that was published over the course of the year 2020.

2020 was an exceptional year by many standards and it illustrates the resilience and capability of the Silicon Divisions to meet new challenges. This is particularly reflected in the number and quality of our scientific publications in 2020. We are able to maintain the same level of publications as in previous years, with a greater number of journal publications making up for the limited opportunities for conference papers due to the cancellation of many events. We note a net increase in number of articles in high impact journals with 17 publications in journals with an impact factor greater than ten compared to 10 in 2019. A few examples amongst these illustrate some of our major topics that are currently being developed.

Again this year, our international collaborative contributions to the rapid progress in the field of Silicon based Quantum technology has been published in Nature Comm., Nature Nanotech., Phys. Rev. X, Appl. Phys Rev and NANO Letters covering aspects from technological developments to design through to cryogenic electronics.

An article in Nature Photonics shows how, in the framework of an international collaboration, our expertise in epitaxy has played an important part in demonstrating ultra-low-threshold continuous-wave and pulsed lasing in tensile-strained GeSn alloys.

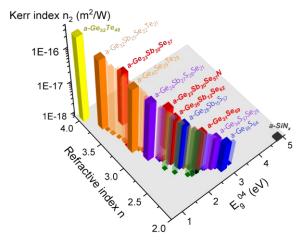

Two articles in Advanced Materials demonstrate how we are working to better understand the fundamentals of chalcogenide materials and exploring applications beyond memory devices. These contributions are strengthened by a theoretical collaborative paper on ionic transport paper published in Nature Communications which pave the way for more rational numerical design of materials.

Finally important developments in advanced nanocharacterisation are showcased in two publications in ACS Nano and Advanced Function Materials.

2020 was a difficult and uncertain year for our interns, PhD students and post-doctoral researchers. Despite this they made a significant contribution to our scientific output in 2020 and participated to make the first all-virtual PhD days event a success. Many PhD vivas, initially planned for 2020 were shifted to 2021 due to contract prolongations and will be included in next year's report, so check back soon!

Lastly we would like to express our gratitude not only to the editorial team and all the authors of the 2020 Scientific Report, but also to the entire department staff who contributed to minimize the impact of the pandemic on our research activities. We hope you find this report instructive and that it may nurture the seeds of many future collaborations.

# **KEY FIGURES**

475 researchers

176 Industrial residents

131 PhD students in 2020

13 Post-docs in 2020

11000 m<sup>2</sup> of cleanrooms 24/6 operation 700 tools

3000 m<sup>2</sup> Nanocharacterization platform

50 advanced instruments

3 CEA institutes (LETI, LITEN, IRIG) working together

22 Joint Research Agreements with Industry

143 patents filed in 2020

1455 patents in portfolio

**405** Scientific communications in 2020

# SCIENTIFIC ACTIVITY

#### **Publications**

405 publications in 2020 (WoS, SCOPUS, ACM) 170 international conference communications in 2020.

#### Prize and awards

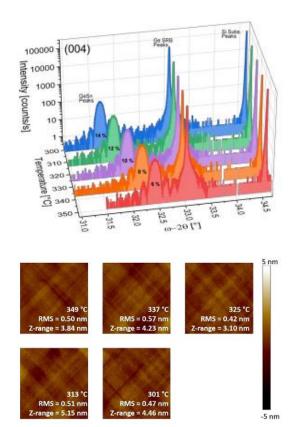

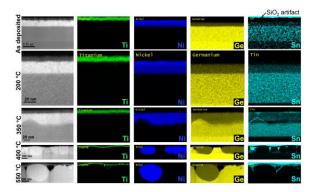

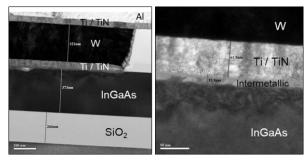

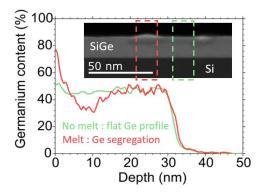

ECS PRIME 2020, Best Paper Award in SiGe, Ge and related compounds session "Analysis of Sn behavior during Ni/GeSn solid-state reaction by correlated X-ray diffraction, atomic force microscopy, and ex-situ/in-situ transmission electron microscopy". A. Quintero et al.

Best paper of the 2020 Electronics System-Integration Technology Conference (ESTC) "Dieto-Wafer 3D Interconnections Operating at Sub-Kelvin Temperatures for Quantum Computation", C. Thomas et al.

Winners of the 2020 3D InCites Awards as "Research Institute of the Year:

https://www.3dincites.com/2020/02/and-the-winners-of-the-2020-3d-incites-awards-are/

Best paper award "Integrated Variability Measurements of 28nm FDSOI MOSFETs down to 4.2K for Cryogenic CMOS Application", B. Cardoso Paz, et al, 33rd IEEE International Conference on Microelectronic Test Structures (ICMTS), Avril 2020

European Star Award for the project 'REFERENCE' (Grant n° 692477), Mention 'Innovation'

## **Experts**

- 7 International Experts

- 4 Research Directors

- 38 Senior Experts

- 56 Experts

- 27 of them holding an HDR

#### Scientific committees

- National Research Agency committee.

- Technical Program committees of:

IEEE IEDM, IEEE VLSI Technology and Circuits, IEEE IRPS, IEEE TRANSDUCERS, IEEE IMW, IEEE ECTC. **IEEE** ESTC. **IEEE** ESSDERC/ESSIRC, IEEE SISPAD, IEEE 3DIC, IEEE ISSCC, IEEE IITC, AMC, ICSI/ISTDM, ECS Transactions AIMES, JNTE, AVS, Advanced Lithography, FCMN, EMRS Spring, l'E\PCOS, CIMTEC, MRS spring 2021 (symposium BEOL), Plathinium 2021, RAFALD, MAM-2020, European FIB Network Workshop

Invited editor of:

Special Focus Issue on « Phase-Change And Ovonic Materials » at Wiley-PSS:rrl,

« Phase-change memories: materials science,

technological applications and perspectives » J. Phys. D: Appl. Phys,

# Conferences and Workshops organizations

4emes Journées des Spectroscopies d'Electrons (French Workshop on Electron Spectroscopy).

29th Materials for Advanced Metallization 2020 (MAM) Grenoble-2020.

# International Collaborations

Forschungs Zentrum Juelich (Germany), Stanford University (USA),

Caltech (USA),

The University of California (USA),

Fraunhofer institutes (Germany),

Università degli Studi di Ferrara (Italy)

University of Cambridge (GB),

Université Catholique de Louvain (Belgium),

University of California at Berkeley (USA),

Politecnico Di Milano (Italy),

Paul Scherrer Institute (Switzerland),

École Polytechnique Fédérale de Lausanne (Switzerland),

ETH - Zürich (Switzerland),

CNR (Italy),

University of Chicago (USA),

Sherbrooke, University (Canada)

NIMS (Japan), SPring-8 Synchrotron (Japan)

University of Southern Denmark

University Cagliari (Italy),

Institute for Technical Physics and Materials

Science (Budapest),

Hungarian Academy of Sciences (Budapest),

Korea University (Seoul)

Centro universitario FEI (Brazil),

University of Tsukuba (Japan),

AIST (Japan),

Herzen University (St Petersburg, Russia).

IMEC, Leuven (Belgium), EMPA, ETH

(Switzerland),

Mons University (Belgium),

University of Surrey (UK)

Université de Liège (Be)

Universitatea Politehnica din Bucuresti (UPB);

National Physical Laboratory, London (UK)

Elettra Synchrotron, Trieste (Italy)

NSLS-II, Brookhaven Nat. Lab. (USA)

Fondazione Bruno Kessler, Trento (Italy)

Physikalisch-Technische Bundesansalt, Berlin, Germany.

Varsaw University, IHPP (Poland)

01

# **CORE & BEYOND CMOS**

- New advances in 3D VLSI integration through the first demonstration of both low temperature CMOS (500°C) and analog FDSOI devices and 28nm FDSOI FEOL & BEOL stability accros yield

- 7-level-stacked nanosheet GAA transistors for high performance computing

- Modelling variability of silicon spin qubits

- Cryo CMOS electronics for quantum computing ICs: electrical characterization and modeling of 28FDSOI technology

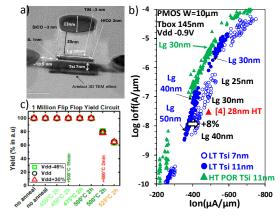

# New advances in 3D VLSI integration through the first demonstration of both low temperature CMOS (500°C) and analog FDSOI devices and 28nm FDSOI FEOL & BEOL stability across yield

#### **RESEARCH TOPIC:**

Low temperature FDSOI transistors, High voltage analog devices, 3D sequential integration, FDSOI devices stability, Yield

#### **AUTHORS:**

C. Fenouillet-Beranger, L. Brunet, C. Cavalcante, L. Brevard, 1W-H. Kim, <sup>2</sup>X. Federspiel, <sup>3</sup>G. Ghibaudo, F. Andrieu, P. Batude

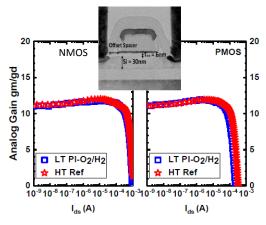

For the first time, the thermal stability of a 28nm FDSOI CMOS technology is evaluated with yield measurements (5Mbit dense SRAM and 1 Million Flip-flops). It is shown that 500°C 2h thermal budget can be applied on a digital 28nm circuit including Cu/ULK BEOL without yield nor reliability degradation. In parallel, the first FDSOI CMOS transistors with Simonocrystalline channel have been fabricated at a temperature below 500°C. Regarding analog devices, we built an original stackable 2.5V device on FDSOI with analog performance comparable to high temperature (HT) reference and passing the PBTI reliability criteria. All these results pave the way for high-performance (HP) digital and analog 3D sequential CMOS integration with the introduction of Cu/ULK BEOL between tiers.

SCIENTIFIC COLLABORATIONS: <sup>1</sup>Samsung electronics, Gyeonggi-do (South Korea); <sup>2</sup>STMicroelectonics, Crolles (FR); <sup>3</sup>IMEP-LAHC, Grenoble (FR).

#### Context and Challenges

3D sequential integration becomes more and more attractive for more Moore and more than Moore applications. However, one of the most important challenge is to implement at low temperature (LT≤500°C) HP CMOS digital devices and analog devices for the upper level, without degrading the bottom one previously integrated. The goal of this study is to demonstrate the feasibility of both LT digital and analog FDSOI devices through relevant electrical Figure Of Merit. Finally, 28nm FDSOI transistors stability is studied versus industry yield characterization.

#### Main Results

The thermal stability of both BEOL Cu/ULK interconnects and FEOL devices upon additional TB has been investigated, with anneal after M8 level. The characterization of Time to Breakdown of BEOL dielectrics show no degradation after 500°C anneal and no degradation of the SRAM yield even at 525°C 2h [1]. FDSOI CMOS transistors with Si-monocrystalline channel have been fabricated below 500°C [2] with HP PMOS and first functional RO (FO1) and LT SRAM bitcells. We built an original stackable 2.5V device on FDSOI enabling to conclude on the feasibility of stacking HV analog devices in 3D VLSI Integration for More-than-Moore applications [3].

Thanks to this first LT 500°C CMOS demonstration and 500°C 2h Cu/ULK BEOL stability, a full 3D sequential Integration with Intermediate BEOL should be demonstrated. The analog LT HV devices can be used for sensor read out operation, paving the way to ultraminiaturized smart sensor arrays.

Figure 1: LT digital lon/loff & Yield [1-2]

Figure 2: FDSOI analog gain (2.5V) [3]

- C. Cavalcante et al., IEEE Symposium on VLSI Technology, 2020, https://doi.org/10.1109/VLSITechnology18217.2020.9265075

- [2] C. Fenouillet-Beranger et al., IEEE Symposium on VLSI Technology, 2020, https://doi.org/10.1109/VLSITechnology18217.2020.9265092 [3] C. Cavalcante et al., IEEE International Symposium on VLSI-TSA, 2020, https://doi.org/10.1109/VLSI-TSA48913.2020.9203691

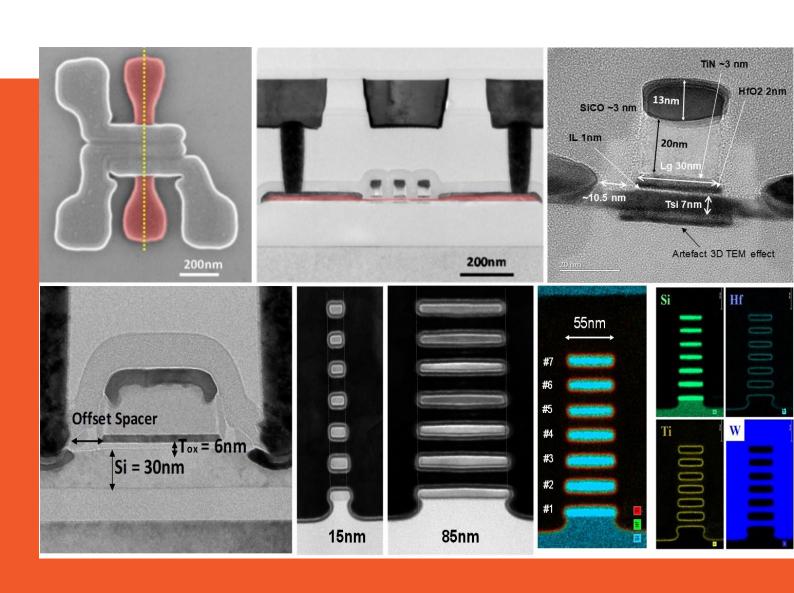

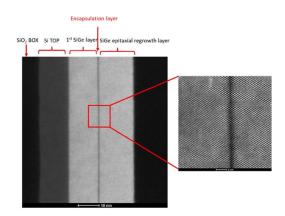

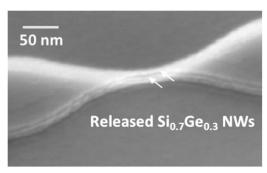

# 7-level-stacked nanosheet GAA transistors for high performance computing

#### **RESEARCH TOPIC:**

CMOS, sub-5 nm node, VLSI, Gate-All-Around, Nanosheet, Nanowires

#### **AUTHORS:**

B. Previtali, C. Vizioz, J.-M. Hartmann, J. Sturm, C. Perrot, Ph. Rodriguez, A. Grenier, F. Andrieu, and **S. Barraud**.

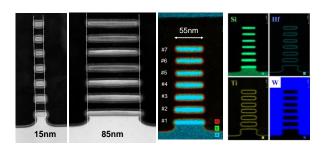

In this work, CEA-Leti experimentally demonstrates, for the first time, gate-all-around (GAA) nanosheet transistors with a record number of stacked channels. Seven levels stacked nanosheet (NS) GAA transistors fabricated using a replacement metal gate process, inner spacer and self-aligned contacts show an excellent gate controllability with extremely high current drivability (3 mA/µm at VDD = 1 V) and a 3× improvement in drain current over usual 2 levels stacked-NS GAA transistors.

#### Context and Challenges

Until now, scaling of FinFET (FF) technology has involved smaller fin width with taller fin and smaller fin pitch (FP) in order to maximize the ratio Weff/FP (with Weff defined as the effective channel width). However, further fin width (and FP) reduction with even more current drivability is complex from the processing and variability points of view. This is the reason why Gate-All-Around (GAA) technology is today proposed for sub-5nm nodes. In addition to have a better gate control (vs FF), GAA transistors offer higher DC performance thanks to higher Weff. The wide range of NS width also provides more design flexibility, which is not possible for FF. In order to improve the current performance of GAA transistors, we explored a new performance lever by increasing significantly the Weff/footprint ratio. Increasing the stacked layers and targeting 7-levelsstacked NS increases process complexity, but the beneficial impact of NS effect is significantly improved while keeping a relaxed FP and lower aspect ratio (vs FF) for fin patterning.

#### Main Results

For the first time, seven levels stacked NS GAA transistors are fabricated using a replacement metal gate process, inner spacer and self-aligned contacts. The backbone of our process flow remains very similar to the one used for FinFET, with nevertheless some extra work on specific modules. The fabrication starts with the epitaxial growth of 150 nm thick Si0.7Ge0.3/Si multilayers (with 7 silicon layers). Thanks to an optimized patterning process, tall and straight (SiGe/Si) fins are fabricated. In fig. 1, we show that a wide range of NS width can be considered (between 15 nm and 85 nm). After that, a challenging etching of SiO2/Poly-Si dummy gates on tall (SiGe/Si) fins is successfully performed. Then, a selective etch of the SiGe layers is performed beforehand to have SiN inner spacers. A lateral growth of in-situ phosphorus-doped Si was carried out to have thick enough S/D. The process then continued with the dummy-gate removal, the release of Si NS, the HfO2/TiN/W deposition and the self-aligned-contacts.

Thanks to the GAA architecture, gate controllability is very

efficient even for wide NS. An excellent immunity to short-channel-effect is demonstrated with a subthreshold slope lower than 70 mV/dec and a DIBL lower than 20 mV/V. In comparison to NS GAA transistors integrating two stacked channels, the seven-channel devices exhibit a threefold improvement in drive current. Thanks to higher Weff/footprint, NS outperform FF transistors with an IODSAT up to 5 mA/µm. This clearly shows the benefit of increasing the number of stacked channels to boost DC performances.

Figure 1: GAA NS FET with 7 stacked Si channels

#### Perspectives

Further developments are still ongoing in order to improve the performance of GAA transistors. But alternative applications are also considered, such as the co-integration of GAA stacked nanosheet transistors with 3D resistive RAMs.

RELATED PUBLICATIONS:

[1] S. Barraud et al., 2020 IEEE Symposium on VLSI Technology, 2020, https://doi.org/10.1109/VLSITechnology18217.2020.9265025

## Modelling variability of silicon spin qubits

#### **RESEARCH TOPIC:**

Quantum information, silicon spin qubits, modeling of materials and devices

#### **AUTHORS:**

L. Hutin, B. Martinez Diaz, B. Venitucci, J. Li, V. Michal, G. Troncoso Fernández-Bada, S. de Franceschi, M. Vinet, Y.M. Niquet

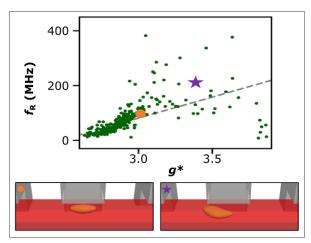

Modeling is a major challenge for quantum computing in silicon and shall help to design the devices and provide support for the interpretation of the experiments, and for the exploration of the physics of these complex devices. New numerical models were developed to simulate silicon-on-insulator qubits and extract the impact of the different sources of variability on the qubit figures of merit.

SCIENTIFIC COLLABORATIONS: <sup>1</sup>Institut Néel (CNRS)

#### Context and Challenges

Spin qubits in silicon are attracting much interest owing to the very long spin lifetimes and incomparable technological knowhow in this material. The qubit information is stored in the spin of carrier(s) trapped in quantum dots. Silicon-on-Insulator (SOI) is one of the appealing platform to realize such qubits: quantum dots are etched in a thin silicon film on SiO2 and controlled by a set of gates. This interplay between structural and electrostatic confinements allows, in particular, to reduce the number of gates per device. These SOI qubits are compatible with scalable CMOS fabrication and are developed in 1D and 2D topologies.

The implementation of a realistic quantum computing device will require quantum error correction protocols to ensure the protection of the quantum information against noise. This usually comes with a large overhead in qubit number that will imply a large scale integration of MOS devices. Because of this high number of devices and the very small energy scales implied, variability management is a major issue that will drive the choice of future architectures [1].

#### Main Results

We have numerically simulated how variability would impact some key figures of merit of spin qubits, for instance the gyromagnetic factor, determining the excitation frequency of the qubits at a given magnetic field (Larmor frequency), and the Rabi frequency, determining the qubit control speed [2]. We studied more specifically the impact of the Si/SiO2 interface roughness and the density of interface traps. The study cover the case of hole spin qubits (with a control mediated by the intrinsic spin-orbit interaction) and electron spin qubits (with an artificial spin-orbit interaction induced by a micro-magnet). In both cases, charge disorder is the main source of variability and is significantly larger for hole qubits. The results are Illustrated by the figure below highlighting distribution of Zeeman splittings (É<sub>Z</sub>=g\*μ<sub>B</sub>B) and Rabi frequency f<sub>R</sub> for different charge disorders and iso-surfaces of squared wave functions for two different configurations.

Impact of interface traps on hole gubits

#### Perspectives

Important aspects such has a quantitative description of valley splitting, spin-orbit coupling or paramagnetic defects remain extremely complex to model. In order to address these challenges, the current models should be complemented with advanced ab initio modeling of materials, interfaces and defects. Such calculations, which are "at or beyond the state-ofthe-art", require huge computational facilities, but shall be achievable within the next few years.

#### RELATED PUBLICATIONS:

[1] M. Vinet et al., Bulletin of the American Physical Society 65 (1), 2020, http://meetings.aps.org/Meeting/MAR20/Session/J17.1 [2] Y. M. Niquet et al., IEEE International Electron Devices Meeting (IEDM), 2020, https://doi.org/10.1109/IEDM13553.2020.9371962

# Cryo CMOS electronics for quantum computing ICs: electrical characterization and modeling of 28FDSOI technology

#### **RESEARCH TOPIC:**

28nm FDSOI CMOS transistors, cryogenic temperatures characterization, quantum information

#### **AUTHORS:**

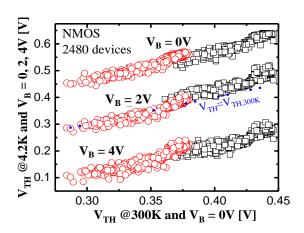

B. Cardoso Paz, G. Ghibaudo<sup>1</sup>, E. Vincent<sup>2</sup>, G. Billiot, M. Vinet, S. de Franceschi, T. Meunier<sup>3</sup>, F. Gaillard, M. Cassé

28nm FDSOI technology is thoroughly electrically characterized aiming at cryogenic applications. Electrostatics, transport, variability and self-heating are evaluated and compared lowering temperature down to 4.2K. FDSOI versatility is shown over a wide temperature range of operation, as the back gate tuning efficiency is preserved at low temperatures. Insights on back gate bias behavior at room and low temperature are obtained. In particular intersubband scattering have been evidenced and modeled at low temperature, with a possible impact for analog designers. The first statistical results ever published on FDSOI variability at 4.2K, using an addressable matrix of transistors, provide valuable information for future compact modeling and circuit design.

SCIENTIFIC COLLABORATIONS: 1 CNRS IMEP-LAHC, 2 STMicroelectronics, 3 CNRS Institut Néel

#### Context and Challenges

To design efficient quantum computers, high performance and low power control electronics in the vicinity of the qubits is a need, i.e. with operation temperatures ranging from 4.2K down to well below 1K. FDSOI technology appears as a valuable solution for the co-integration of qubits and control electronics, taking advantage of its threshold voltage tunability allowed by the back bias. So far however, advanced CMOS nodes have not been extensively explored for deep cryogenic operation. Because these aspects are essential for the development of compact models and robust design tools, this work presents extensive electrical characterization and analysis of 28nm FDSOI MOSFETs down to 100mK, with regard to devices electrostatics, variability or thermal effects.

#### Main Results

We have demonstrated that FDSOI transistors are fully operating down to 100mK, including the ability to tune the threshold voltage with the same efficiency as at room temperature (RT) thanks to the back bias [1]. Improved ON current (from x5.6 on long devices to x1.6 on short NMOS) OFF current (below our equipment accuracy <1fA) and subthreshold slope (as low as 9mv/dec.) contribute to the very good performances of FDSOI technology at cryogenic temperature, as demonstrated in a quantum integrated circuit on a single chip in industrial 28nm FDSOI CMOS technology (https://doi.org/10.1109/ISSCC19947.2020.9063090). Statistics and mismatch analysis were carried out down to 100mK, through an automated measuring system implemented with an on-chip multiplexed matrix arrangement of addressable transistors arranged in matched pairs (see Figure 1) [1,2]. We thus demonstrated for the first time that 28nm FD-SOI outperforms other CMOS technologies at low temperature (LT) in variability and that the latter remains low enough so that its impact could be mitigated for circuit operation at LT. Additional feature appear on the drain current in long channel devices when forward back bias is applied, as the consequence of a discontinuity in the mobility due to intersubband scattering at LT

[3]. This behavior, specific to thin film devices, has to be taken into account into future cryo-CMOS compact models. Low frequency noise (LFN) has also been investigated down to 4.2K; our results have shown that LFN can be well described by the carrier number with correlated mobility fluctuations model

Figure 1: Comparison of VTH at 4.2K and RT.

#### Perspectives

These results provide a ground for future compact models at LT and the first guidelines for design optimization at deep cryogenic temperatures. Same work has to be done on RF electrical characterization, for which even less data have been published so far.

- [1] B. Cardoso Paz et al., Symposium on VLSI Technology, 2020, <a href="https://doi.org/10.1109/VLSITechnology18217.2020.9265034">https://doi.org/10.1109/VLSITechnology18217.2020.9265034</a>

[2] B. Cardoso Paz et al. ICMTS, 2020, <a href="https://doi.org/10.1109/ICMTS48187.2020.9107906">https://doi.org/10.1109/ICMTS48187.2020.9107906</a> (Best paper award)

[3] M. Cassé et al., Appl. Phys. Lett., 2020, <a href="https://doi.org/10.1109/ICMTS48187.2020.9107906">https://doi.org/10.1109/ICMTS48187.2020.9107906</a> (Best paper award)

[4] B. Cardoso Paz et al., IEEE Trans. Electron Devices, 2020, <a href="https://doi.org/10.1109/ICM.2020.3021999">https://doi.org/10.1109/ICM.2020.3021999</a>

02

### **MEMORIES**

- Exploiting resistive memory randomness with Bayesan neural networks

- High density RRAM arrays for neuromorphic applications based on 3D monolithically Integrated technology and multi-level programming strategies

- 3D RRAM with Gate-All-Around stacked nanosheet transistors for in-memorycomputing.

- Phase change memory: electro-thermal and phase field simulations to explore Innovative PCM architectures and PCM crystallization mechanisms

- Ovonic threshold switching and phase-change memory devices for storage class memory

- Co-integration of resistive memories with backend selectors for future high energy efficient systems

- BEOL compatibility of Si:HfO<sub>2</sub> ferroelectric films and demonstration of nanosecond laser anneal to boost their remanent polarization

# Exploiting resistive memory randomness with Bayesian neural networks

#### **RESEARCH TOPIC:**

Development of resistive memory based Bayesian neural network hardware and machine learning algorithms

#### **AUTHORS:**

T. Dalgaty, N. Castellani, D. Querlioz<sup>1</sup>, E. Vianello

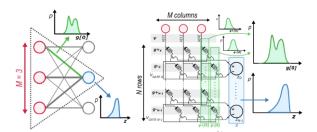

For decades, resistive memory devices (RRAM) have been heralded as a means of reducing the energy requirements of neural networks deployed on edge devices. However, their adoption in industrial neural network products remains challenging and scarce. This is because the intrinsic random and noisy properties of RRAM do not offer the high-precision programmable memory element demanded by traditional "deterministic" neural networks. Bayesian neural networks, whose synapses and neurons are described by probability distributions, can in contrast actively harness this randomness. This emerging research activity aims to explore how these intrinsic 'non-ideal' device properties can be leveraged in low-energy Bayesian neural network hardware and learning algorithms.

SCIENTIFIC COLLABORATIONS: 1 CNRS, Université Paris-Saclay

#### Context and Challenges

Resistive memory devices efficiently implement the dot-product operation that underpins neural network models. However, neural networks and learning algorithms implemented using RRAM perform poorly compared to software counterparts realized on microprocessors. The reason for this is that "deterministic" neural networks require memory elements that can be precisely controlled - intrinsically RRAM doesn't offer this.

#### Main Results

We argue that it is the modelling approach, not the technology, that is the problem. Synaptic parameters and neurons in **Bayesian neural networks** are described using random variables. RRAM effectively also behave as nanoscale, physical random variables. Could RRAM and Bayesian neural networks be a better pairing? In two recent publications this year, we have argued this is the case [1,2]. Notably we demonstrated that the random properties of RRAM could be harnessed to by reduce by five orders of magnitude the energy required in implementing Bayesian machine learning algorithms.

#### Perspectives

Bayesian neural networks based on RRAM offer a means of bringing inference and learning to extremely energy and memory constrained edge devices. Our attention is turning towards the question of edge learning systems might operate given that labelled datasets do not exist at the edge and how Bayesian learning algorithms can be applied in the unsupervised, reinforcement and self-supervised settings.

Figure 1: An RRAM-based Bayesian neuron

Figure 2: Ideal properties for Bayesian learning

- [1] T. Dalgaty, Advanced Intelligent Systems, 2021, https://doi.org/10.1002/aisy.202000103

- [2] T. Dalgaty, Nature Electronics, 2021, https://doi.org/10.1038/s41928-020-00523-3

# High density RRAM arrays for neuromorphic applications bases on 3D monolithically integrated technology and multi-level programming strategies

#### **RESEARCH TOPIC:**

Emerging Non-Volatile Memory Circuits, 3D Integration, Neuromorphic Systems

#### **AUTHORS:**

E. Esmanhotto, L. Brunet, N. Castellani, JM. Portal<sup>1</sup>, S. Mitra<sup>3</sup>, F. Andrieu, C. Fenouillet-Beranger, E. Nowak, E. Vianello.

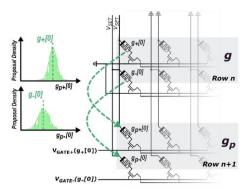

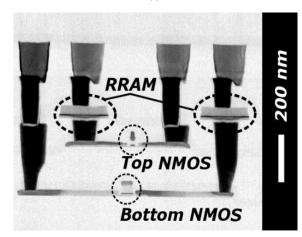

CEA-Leti showed, for the first time, a 3D monolithically integrated multiple 1T1R Resistive RAM (RRAM). Our recent studies combines the mentioned new stack technology with a Multi-Level Cell (MLC) programming strategy allowing up to 3.17 bits to be stored in a single RRAM device. The proposed high density solution is extensively tested on a 4 kb 1T1R planar array for both memory and neuromorphic applications and the results shows that neuromorphic applications seems to be better suited for MLC programming because standard memory applications suffers from overlaps between programmed levels after the conductance relaxation effect.

SCIENTIFIC COLLABORATIONS: <sup>1</sup>Aix-Marseille Université, IM2NP, Marseille (FR), <sup>2</sup>Université Paris-Saclay, CNRS, Palaiseau (FR), 3Stanford University, Stanford, CA (USA)

#### Context and Challenges

One of the main challenges for RRAM-based memory arrays is achieving high density of storage. For standard memory applications, high density is fundamental to place the RRAM technology among standard and scalable CMOS. Although, RRAM based memory circuits are also good for neuromorphic hardware thanks to the capability of RRAMs to perform a MAC operation naturally. Nevertheless, for neuromorphic applications, high density is also necessary in order to enhance performance of the system.

The bottleneck of the 1T1R structure remains the size of the access transistor that comes along with the RRAM device. The access transistor has to be big enough to drive the current necessary to program the RRAM and the 1T1R total surface is then appropriated by a transistor with a size that is hard to reduce. To overcome this scenario, it is possible to combine CEA-Leti latest advances on 3D stack integration and Multi-Level Cell (MLC) programming to achieve a high-density 3D monolithically integrated multiple 1T1R cell.

Our solution to improve RRAM density consists in combining a new 3D monolithically integrated multiple 1T1R (figure 1) developed at CEA-Leti with our own Multi-Level Cell (MLC programming strategy.

The 3D monolithically integrated multiple 1T1R might achieve 1.5X more density when compared to a standard planar 1T1R cell and features two HfO2 based RRAM fabricated on the BEOL with one of the RRAM connected to the bottom transistor and another connected to the top transistor. This 3D integrated 1T1R cell preserves the same behavior as a standard planar 1T1R cell.

The adopted MLC programming strategy was extensively studied for memory and neuromorphic applications using a 4 kb planar array. We show that it is possible to program up to nine conductance levels (equivalent to 3.17 bits) per RRAM device relying on the cycle-to-cycle variation of the RRAM devices while controlling the programming current which remains as low as possible to keep low power.

Standard memory applications suffers from the overlap between adjacent levels after programming due to the conductance relaxation effect. For memory applications, the MLC strategy is limited to four conductance levels (2 bits) in order to keep an acceptable BER. On other hand, we proposed a Neural Networks seems to be resilient to conductance relaxation, taking full advantage of the nine conductance levels. On this scenario, we improve by 4.75x the density of a RRAM 1T1R cell for Neural Network applications.

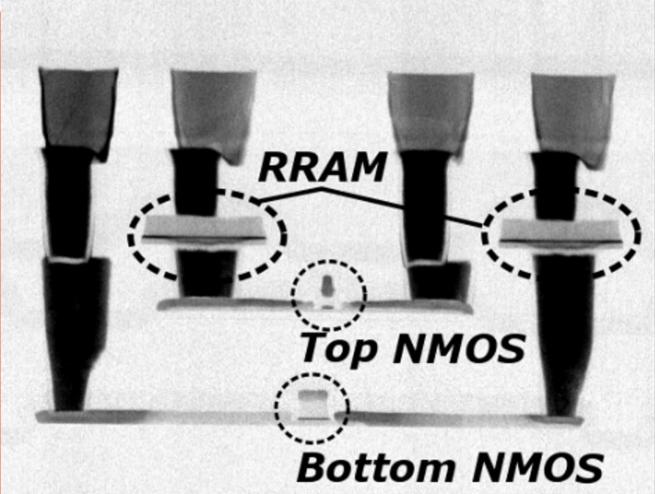

Figure 1: 3D structure with two CMOS and two RRAM.

#### Perspectives

Our research will continue to investigate MLC programming as a key feature of RRAM with the potential of leading us to further demonstrations of high performance and high-density neuromorphic hardware. Different design solutions might be proposed to handle the MLC programming strategy better while new CEA-Leti stack technologies will continuously be explored.

- [1] E. Esmanhotto et al., 2020 IEEE International Electron Devices Meeting (IEDM), 2020, https://doi.org/10.1109/IEDM13553.2020.9372019

[2] C. Fenouillet-Beranger et al., 2020 IEEE Symposium on VLSI Technology, 2020, https://doi.org/10.1109/VLSITechnology18217.2020.9265092

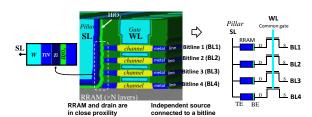

# 3D RRAM with Gate-All-Around stacked nanosheet transistors for in-memory-computing

#### **RESEARCH TOPIC:**

Resistive RAM, HfO<sub>2</sub>-based OxRAM, qate-all-around, nanosheet, junctionless, in-memory-computing

#### **AUTHORS:**

M. Ezzadeen, T. Dubreuil, N. Castellani, J.M. Hartmann, B. Previtali, J.M. Portal<sup>1</sup>, G. Ghibaudo<sup>2</sup>, F. Andrieu, and **S. Barraud**.

This work explores a novel 3D one transistor / one RRAM (1T1R) memory cube. The proposed architecture integrates  $HfO_2$ -based OxRAM with select junctionless (JL) transistors based on Gate-All-Around stacked NanoSheet (NS) technology. Extensive characterization of JL transistors and OxRAMs is performed to show their ability to be co-integrated inside a same 1T1R memory cell. We show that a proper engineering of JL GAA transistors can result in compliance currents which are high enough to address OxRAM arrays whose memory window reaches HRS/LRS = 20 up to  $10^4$  cycles. This new architecture, which offers a high write and read parallelism, can be leveraged for in-memory-computing (IMC).

SCIENTIFIC COLLABORATIONS: <sup>1</sup> University Aix Marseille, CNRS, IM2NP, Marseille, France, <sup>2</sup> University Grenoble Alpes, IMEP-LAHC, 38000 Grenoble, France.

#### Context and Challenges

Today, storage-class memories like high-density 3D crossbar RRAM are promising for applications requiring a large amount of on-chip memory. RRAM is a leading candidate due to its high density, good scalability, low operating voltage, and easy integration with CMOS devices. Another attractive aspect of RRAM is their ability to perform primitive Boolean logic operations for in-memory and neuromorphic computing. However, if the 1T1R design is the most reliable architecture for IMC, the cell size remains limited by the conventional access transistor. This is why, in this work, our 1T1R architecture benefits from the high density of vertically stacked NS transistors which feature excellent scalability. This novel 1T1R 3D RRAM architecture is competitive from the crossbar density point of view, while getting rid of any sneak path current, enabling large-scale IMC.

#### Main Results

Our 3D 1T1R architecture is derived from our GAA CMOS structure and process flow; the main difference is that each horizontal GAA channel features an independent source connected to a BitLine (BL) and a drain directly connected to a pillar of RRAM memory cells (figure 1) [1]. First, we study the performance of GAA JL transistors used as selector. Preliminary TCAD simulations enabled us to find a good compromise between high performance and good electrostatic control. Then, we fabricated nMOS JL transistors with one level of NS. They exhibit an  $I_{ON}$  current of 120  $\mu$ A at  $V_{DS} = 1.3 \text{ V}$ ,  $V_{GS} = 1.5 \text{ V}$ ,  $L_G = 60 \text{ nm}$  and W = 50 nm, which should be translated into a compliance current  $I_{\text{CC}}$  close to 150 $\mu A$  at W = 80 nm (targeted width of our select GAA transistors). We also checked that the local variability is not strongly degraded with JL transistors and that they can be cycled up to  $V_{\text{DD}} = 2 \text{ V}$ more than 107 times with negligible electrical characteristic modifications [2]. Similarly, we characterized 4kbits 1T1R RRAM arrays based on TiN bottom electrode / 5 nm  $HfO_2/5$ nm  $\operatorname{Ti}/\operatorname{TiN}$  top electrode integrated in the BEOL with select transistors based on 130nm CMOS technology. Electrical characterization of 4kbits OxRAM arrays shows a large memory window (HRS / LRS = 20) up to  $10^4$  cycles with a current compliance of  $150\,\mu\text{A}$ , compatible with the performances of our JL transistors. Finally, we experimentally demonstrate scouting logic operations capability with 2 operands, which should be extended to 4 operands thanks to an original two cells/bit "double coding" scheme assessed by SPICE simulations [3]. We evidenced that this computing scheme which is 2 times more energy efficient than a write-verify approach can be a good option to perform *in-situ* logic operations.

Figure 1: 1T1R OxRAM memory cell

#### Perspectives

Technological development of modules are still ongoing in order to build and explore this 1T1R 3D RRAM architecture. This work is also supported by SPICE simulation to investigate the interest of this novel architecture for IMC.

- [1] S. Barraud et al., 2020 IEEE International Electron Devices Meeting (IEDM), <a href="https://doi.org/10.1109/IEDM13553.2020.9371982">https://doi.org/10.1109/IEDM13553.2020.9371982</a>

[2] D. Bosch et al. 2020 IEEE Symposium on VLSI Technology, <a href="https://doi.org/10.1109/VLSITechnology18217.2020.9265036">https://doi.org/10.1109/VLSITechnology18217.2020.9265036</a>.

- [2] D. Bosch et al. 2020 IEEE Symposium on VLSI Technology, <a href="https://doi.org/10.1109/VLSITechnology18217.2020.9265036">https://doi.org/10.1109/VLSITechnology18217.2020.9265036</a>.

[3] M. Ezzadeen et al. IEEE Transactions on Electron Devices, vol. 67, no. 11, pp. 4626-4630, Nov. 2020, <a href="https://doi.org/10.1109/TED.2020.3020779">https://doi.org/10.1109/TED.2020.3020779</a>.

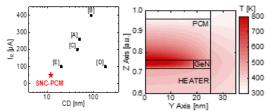

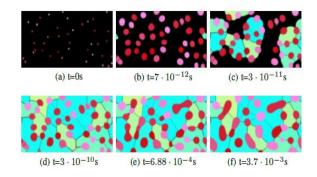

# Phase change memory: electro-thermal and phase field simulations to explore innovative PCM Architectures and **PCM Crystallization Mechanisms**

#### **RESEARCH TOPIC:**

PCM, Ge rich GST, Innovative PCM, Phase Change Mechanism, Electro-thermal and Phase Field simulations, Physical Characterization

#### **AUTHORS:**

O. Cueto, G. Navarro, E. Nolot, L. Prazakova, A.L. Serra, R. Bayle<sup>1,2,4</sup>, M. Plapp<sup>2</sup>, C. Vallee<sup>3</sup>, M.C. Cyrille

Phase-Change Memory (PCM) is one of the most promising innovative non-volatile memory technologies. We report on PCM TCAD simulation activity at the CEA-Leti that provides guidelines to technological development but also insight in complex physical crystallization mechanisms. The realizations we report on also illustrates the complementarity of TCAD simulation activity with electrical characterization and advanced physical characterization activities at CEA-Leti.

SCIENTIFIC COLLABORATIONS: 1 STMicroelectronics, 2 LPMC CNRS-Ecole Polytechnique, 3 CNRS-LTM, 4 CEA-Leti.

#### Context and Challenges

PCM entered the market addressing Storage Class Memory and it is in sampling within Microcontrollers for Automotive applications. PCM architecture optimization and crystallization dynamics understanding are still required.

#### Main Results

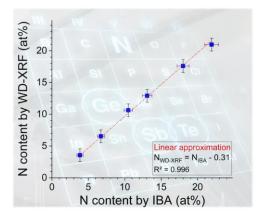

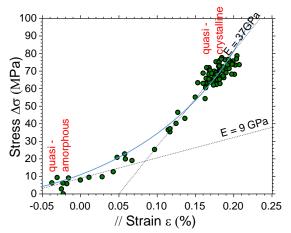

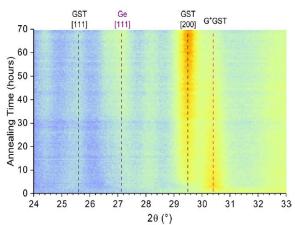

We demonstrated that a lithography independent Self-Nano-Confined PCM enables programming down to 50 □ A and endurance more than 108 cycles in a 4kb array (Figure 1a). 3D Electro-thermal simulations highlighted that such low current density is due to a better thermal confinement (Figure 1) [1]. With LPMC and STMicroelectronics, we developed a tool with the multiphase field method to simulate phase changes in Ge rich GST [2]. It captures both the emergence of a two-phase polycrystalline layer starting from an amorphous layer (Figure 2) and the melting and recrystallization during the SET and RESET operations in a "wall" type PCM [2]. Experimental results (XRD, FTIR and Raman) confirm the emergence of two distinct crystalline phases: Ge/GST[3].

#### **Perspectives**

A full coupling of the multiphase field model with the electrothermal solver will be implemented in collaboration with advanced physical characterization team and atomistic simulation team. Microstructure of the material modifies the current and the temperature through the PCM. In order to include such heterogeneities, the equations for electric and heat conduction need to be resolved with the same spatial resolution as the phase-field model, with phase dependent properties.

- [A] J.I. Lee et al, VLSI 2007

- [B] R. Anunziata et al. IEDM 2009

- [C] G. Servalli, IEDM 2009

- [D] S. Hanzawa et al, ISSCC 2007

- [E] Y. Choi et al, ISSCC 2012

Figure 1: Left) SNC vs other PCM Right) T SNC

Figure 2: Crystallization (pink: Ge, green: GST)

- [1] A.L. Serra et al, Transactions on Electron Devices (2020), <a href="https://doi.org/10.1109/TED.2020.3044267">https://doi.org/10.1109/TED.2020.3044267</a>

[2] R. Bayle et al, Journal of Applied Physics (2020), <a href="https://doi.org/10.1063/5.0023692">https://doi.org/10.1063/5.0023692</a>

- [3] L. Prazakova et al, Journal of Applied Physics (2020), https://doi.org/10.1063/5.0027734

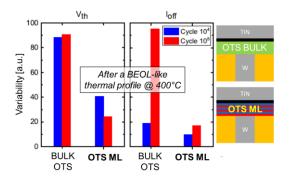

# Ovonic threshold switching and phase-change memory devices for storage class memory

#### **RESEARCH TOPIC:**

Ovonic Threshold Switching (OTS), Phase-Change Memory (PCM), Storage Class Memory (SCM)

#### **AUTHORS:**

C. Laguna, G. Lama, M. Bernard, N. Castellani, S. Abdelkader<sup>1</sup>, G. Navarro

Back-End-of-Line (BEOL) resistive memory technologies demonstrated to be the right enabler for Storage Class Memory (SCM) applications required in modern and future memory-centric architectures. This was possible thanks to the combining of the unique selector features of Ovonic Threshold Switching (OTS) devices, with the reliability and maturity of Phase-Change Memory (PCM). In this framework, we developed and analyzed a new class of OTS devices called "OTS Multilayer" (OTS ML) enabling low electrical properties variability and studied key metrics and reliability analysis protocols in PCM targeting high endurance and high speed and preparing next generation of high density 3D multiple decks Crossbar arrays based on PCM and OTS.

SCIENTIFIC COLLABORATIONS: 1 INSA Lyon

#### Context and Challenges

Storage Class Memory (SCM) became a necessary level of the memory hierarchy with the goal to provide a low read latency, non-volatile and cost effective interface between the memory (DRAM) and the storage (NAND Flash). 3D Crossbar arrays, enabled by BEOL OTS and resistive memory technologies, represent the best candidates for SCM, but they require extremely high endurance and high programming speed.

#### Main Results

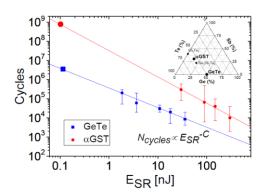

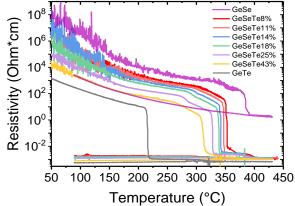

We demonstrated that through a new family of selector devices called "OTS Multi-Layer", we can target the material stability at 400°C and the tuning of the selector switching performances by properly engineering interfaces, thickness and individual layers' stoichiometry. We validated the high variability control of the electrical parameters and a high endurance up to more than 10° cycles (Figure 1) wrt to a standard bulk solution [1]. SCM suitability was investigated in GeTe and GeSbTe based PCM devices, studying and describing their main metrics evolution along cycling. Thanks to the subthreshold conductivity and retention analyses, we provide evidence why GeSbTe alloys can target an endurance of more than 109 cycles at low programming energy (Figure 2), fulfilling SCM requirements [2].

#### Perspectives

Co-integration of best OTS and PCM technologies available in Leti is ongoing, targeting the demonstration of the reliability of the Crossbar arrays and of the new devices architectures developed. This will enable new memory design paradigms and new applications.

Figure 1: Threshold switching and leakage current spread

Figure 2: Endurance performances

- [1] C. Laguna et al, International Memory Workshop (IMW), 2020, https://doi.org/10.1109/IMW48823.2020.9108130 [2] G. Lama, Microelectronic Reliability, 2020, https://doi.org/10.1016/j.microrel.2020.113823

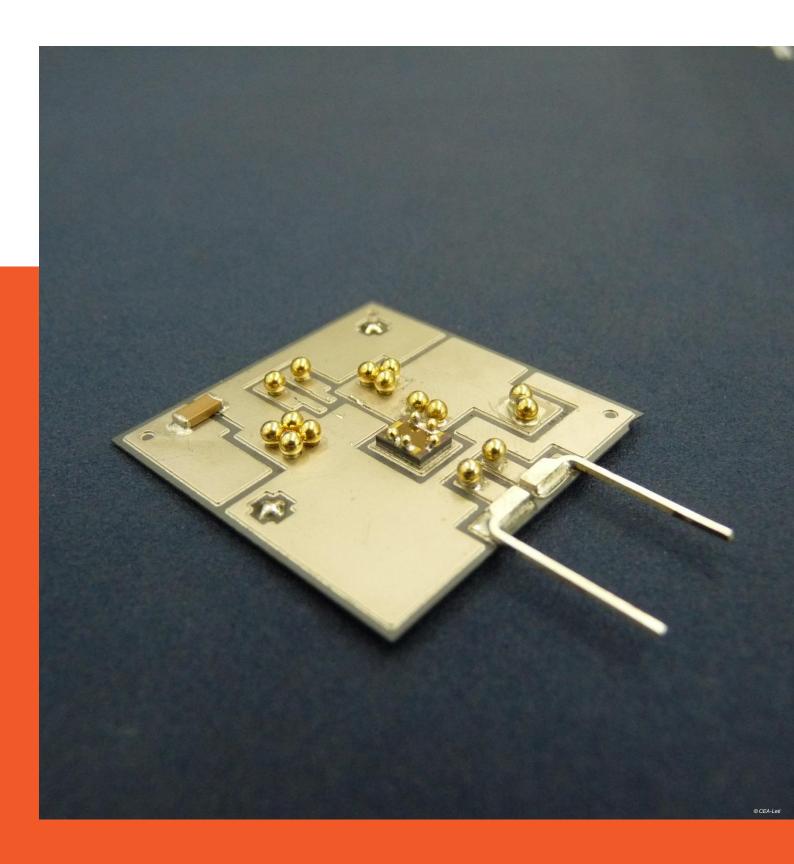

# Co-integration of resistive memories with back-end selectors for future high energy efficient systems

#### **RESEARCH TOPIC:**

Resistive memories, RRAM, 1S1R, crossbar, crosspoint, programming, in memory computing

#### **AUTHORS:**

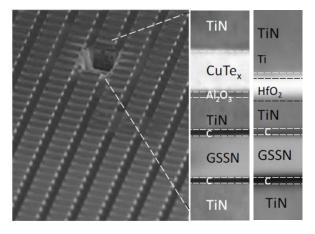

J.M. Lopez, P. Trotti, L. Grenouillet, N. Castellani, J. F. Nodin, G. Navarro, S. Oukassi, G. Pillonnet, C. Carabasse, G. Molas

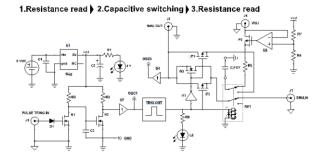

We have developed low voltage operation 1S1R structures composed by resistive memories (RRAM) integrated with a back-end selector which can be adjusted based on the circuit requirements. We also propose an innovative low power charge based RRAM programming scheme. These solutions provide a powerful set for boosting energy efficiency and improving performances like endurance and variability.

SCIENTIFIC COLLABORATIONS: 1 IMEP-LAHC, 2 IM2NP Marseille, 3 INL-CNRS, INSA de Lyon

#### Context and Challenges

Resistive Memories (RRAM) is a promising hardware candidate implementing performant In Memory Computing architectures. Developing dense crosspoint arrays and efficient programming scheme are key enablers to boost the actual RRAM performances.

#### Main Results

We designed two RRAM based crosspoint structures showed forming free behavior, stable 2 decades for lon/loff during 107 cycles and moderate leakage current compatible with 100kB. Playing with the memory and selector stacks, we explore high density integration allowing >1MB crosspoint arrays with low voltage operation on a 28nm core process.

We also developed an innovative programming scheme consisting of discharging a programming capacitor over the memory cell, controlling the maximum energy provided to the The solution was experimentally validated demonstrating the potential to reduce the programming energy of a factor of 10 in comparison with standard writing scheme.

#### **Perspectives**

We are investigating the impact of scaling of RRAM based crosspoints. We are also implementing fully integrated charge based programming scheme on next test vehicles to demonstrate energy and variability gains for future in memory computing systems.

Figure 1: 1S1R and stacks for crosspoint arrays.

Figure 2: Charge based programming circuit board

- [1] G. Molas et al., IEEE International Memory Workshop (IMW), 2020, <a href="https://doi.org/10.1109/IMW48823.2020.9108143">https://doi.org/10.1109/IMW48823.2020.9108143</a>

[2] J. M. Lopez et al., IEEE International Memory Workshop (IMW), 2020, <a href="https://doi.org/10.1109/IMW48823.2020.9108126">https://doi.org/10.1109/IMW48823.2020.9108126</a>

[3] P. Trotti et al., IEEE 33rd International Conference on Microelectronic Test Structures (ICMTS), 2020, <a href="https://doi.org/10.1109/ICMTS48187.2020.9107936">https://doi.org/10.1109/ICMTS48187.2020.9107936</a>

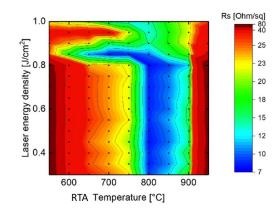

# BEOL compatibility of Si:HfO<sub>2</sub> ferroelectric films and demonstration of nanosecond laser anneal to boost their remanent polarization

#### **RESEARCH TOPIC:**

Ferroelectric  $HfO_2$ , Back End of Line integration, CMOS compatibility, Nanosecond Laser Anneal, Silicon doping

#### **AUTHORS:**

T. Francois, J. Coignus, S. Kerdilès, N. Vaxelaire, C. Carabasse, S. Slesazeck<sup>1</sup>, U. Schroeder<sup>1</sup>, T. Mikolajick<sup>1</sup>, **L. Grenouillet**

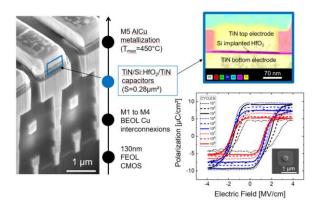

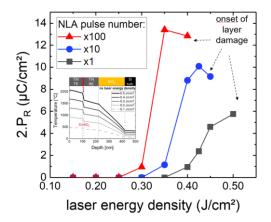

Scaled ferroelectric Si-implanted HfO $_2$  capacitors of 0.28  $\mu$ m² were successfully co-integrated above 130 nm CMOS, demonstrating for the first time BEOL compatibility of this material. Area scaling is shown to improve endurance (10<sup>12</sup> cycles extrapolated at 3 V). Excellent distributions of coercive fields E<sub>C+</sub>, E<sub>C-</sub> and remanent polarization 2·P<sub>R</sub> are reported at wafer scale, as well as excellent data retention at 85 °C. Nanosecond Laser Anneal (NLA) is demonstrated to be extremely powerful to "engineer" ferroelectric film crystallization. Ferroelectric undoped HfO $_2$  is obtained with this technique, and 2.P<sub>R</sub> values > 20  $\mu$ C/cm² are reported for Si:HfO $_2$ , while keeping BEOL compatibility.

SCIENTIFIC COLLABORATIONS: <sup>1</sup>NaMLab gGmbH, Dresden, Germany

#### Context and Challenges

Ferroelectric HfO<sub>2</sub>-based thin films are changing the paradigm of ferroelectric memories, thanks to their CMOS compatibility and potential for scalability. In 2019, our group demonstrated for the first time that scaled Hf0.5Zr0.5O<sub>2</sub>-based ferroelectric capacitors integrated above 130 nm CMOS are compatible with BEOL thermal budget [1,2]. In the following 10 nm Si-doped HfO<sub>2</sub> films, whose crystallization temperature is higher than Hf0.5Zr0.5O<sub>2</sub>, were assessed.

#### Main Results

TiN/Si:HfO $_2$ /TiN capacitors with diameters of 600nm (0.28µm²) were integrated in 130nm BEOL CMOS between M4 and M5. Our approach consists in doping the 10 nm HfO $_2$  film by ion implantation, which facilitates intermixing compared to the conventional ALD doping technique. Ferroelectric behavior is reported with a maximum thermal budget of 450°C for crystallization (Figure 1). Capacitor area downscaling is demonstrated to be beneficial for high endurance (10 $^{12}$  cycles extrapolated at 3 V).

In order to improve further film crystallization in the orthorhombic (ferroelectric) phase, Nanosecond Laser Anneal is demonstrated to be very promising to increase temperature above 1000  $^{\circ}\text{C}$  in the HfO<sub>2</sub>-based film without compromising CMOS integrity (Figure 2).

#### **Perspectives**

These results pave the way to the demonstration of 1T-1C FeRAM memory arrays using ferroelectric HfO $_2$ . In particular, the high endurance demonstrated for HfO $_2$ -based capacitors is promising to bridge the gap toward the  $10^{15}$  cycling requirement.

Figure 1: HfO<sub>2</sub>-based BEOL ferroelectric capacitors

Figure 2: Laser Anneal boosts remanent polarization

- [1] T. François et al., IEEE International Electron Devices Meeting (IEDM), 2019, https://doi.org/10.1109/iedm19573.2019.8993485 [2] L. Grenouillet et al., IEEE Silicon Nanoelectronics Workshop (SNW), 2020, https://doi.org/10.1109/SNW50361.2020.9131648

- [3] L. Grenouillet et al., IEEE Symposium on VLSI Technology (VLSI), 2020, https://doi.org/10.1109/VLSITechnology18217.2020.9265061

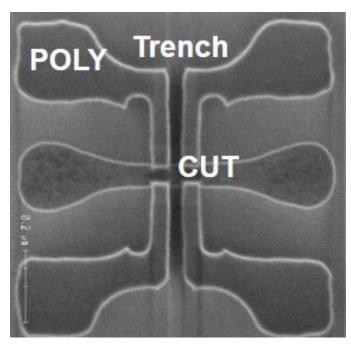

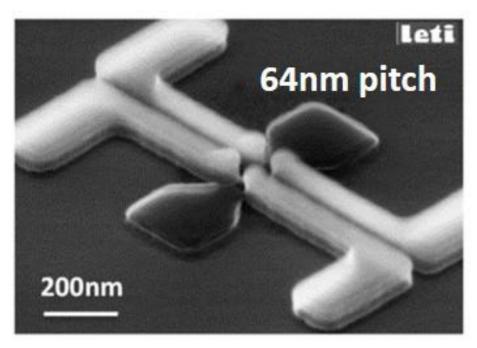

Gate Patterning with (Litho-etch³) triple process Pitch down to 64 nm and OVL spec. <30nm

2D quantum-dot arrays

© CFA-I et

03

## **PATTERNING**

- Immersion lithography on the edge

- Etching impact on the self-assembly and pattern transfer of block copolymers for new advanced patterning approach

- Sub-15 nm multilayer nanopillar patterning for hybrid SET/CMOS integration

- Development of non-conventional chemistries for advanced CMOS spacer patterning

- Hybrid E-beam lithography capabilities for a large field of nanodevices applications

## Immersion lithography on the edge

#### **RESEARCH TOPIC:**

Immersion lithography, 193i, patterning, large field stitching, negative tone development (NTD)

#### **AUTHORS:**

M. Argoud, A. Le Pennec, R. Tiron, C. Comboroure, B. Minghetti<sup>1</sup>, Pui Lam<sup>2</sup>, C. Navarro<sup>3</sup>, M. May, G. Rademaker

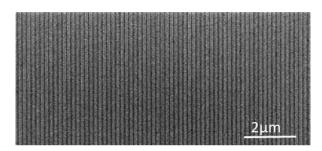

Immersion 193 nm lithography is a mature technology that enables to address new challenges outside the conventional fields of application. For a polarization filter application, a full wafer has been seamlessly exposed with continuous high resolution line/space gratings. A second advanced use case was to implement a negative tone development (NTD) resist to enlarge patterning performance, required for the Directed Self-Assembly (DSA) of lamellar line/space block copolymers (BCP) with a nominal period  $L_0$  of 31.5 nm.

SCIENTIFIC COLLABORATIONS: 1,2 ASML (FR, NL), 3 Arkema (FR)

#### Context and Challenges

Immersion lithography (IL) has been a workhorse semiconductor technology for over a decade. The reticle is usually limited by the field size of 26 mm x 33 mm. For a polarization filter application, the required effective field size was 20 cm by 20 cm consisting of a continuous grating with a CD of 50 nm and a period of 100 nm. This required an unusual field-to-field positioning measurement and control within the same layer, which can be extended to large chips for other applications [1]. A second advanced use case is overcoming the resolution limits of the immersion scanner by means of pitch multiplication by DSA of lamellar BCPs. In order to prevent assembly defects, these polymers need high-quality guides [2].

#### Main Results

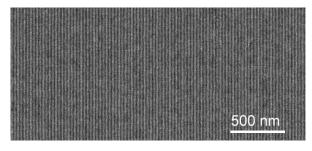

For the polarizer stitching application, a diffraction based overlay (µDBO) target has been developed to measure the stitching alignment between the different exposed fields. The field-to-field stitching performance was measured and corrected by a novel 13-term polynomial model developed by ASML, until a stitching of 1.5 nm (μ+3σ) misalignment was attained. This result was applied to the polarizer case (without µDBO marks) and combined with an aerial image simulation to address stitching artefacts such as line pinching and bulging and to determine the best conditions for continuity. This resulted in a full 300 mm wafer seamlessly exposed with 50 nm CD, 100 nm period line/space gratings [1].

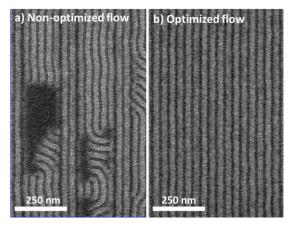

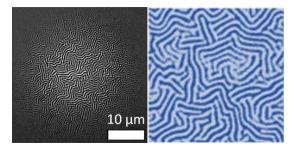

The ACE process for DSA, unique at CEA-Leti is based on the use of spacer double patterning to create the guides for the DSA of 31.5 nm period line/space patterns. Given their sensitivity to the quality of the guiding pattern, IL combined with a negative tone development (NTD) resist has been put in place [2]. The use of a mask with large-scale features has been a key enabling factor to decrease alignment defects of block copolymers by three orders of magnitude to 10<sup>4</sup> cm<sup>-2</sup>.

Figure 1: Seamless stitching of 4 fields (CD = 50 nm

Figure 2: Alignment of block copolymers (CD = 16 nm

#### **Perspectives**

The seamless stitching approach developed can be used for imagers with high-resolution features, ultra-large die electronics and becomes necessary for high-NA (0.55) EUV lithography. NTD resists will be pursued for the most demanding of patterning applications sensitive to patterning variations, such as silicon quantum computing and low-loss photonic applications.

- [1] M. May et al. Proc. SPIE 11325 (2020), https://doi.org/10.1117/12.2552012 [2] G.J. Rademaker et al, Proc. SPIE 11326 (2020), http://doi.org/10.1117/12.2552003

## Etching impact on the self-assembly and pattern transfer of block copolymers for new advanced patterning approach

### **RESEARCH TOPIC:**

Etching for Directed Self-Assembly (DSA) application

### **AUTHORS:**

M. G. Gusmão Cacho, K. Benotmane, P. Pimenta-Barros, C. Navarro<sup>1</sup>, K. Sakavuyi<sup>2</sup>, N. Possémé

Directed Self-Assembly (DSA) of block copolymers is an advanced patterning technique being investigated to target small and dense patterns for the future technological nodes. The most important aspect of this technique is to obtain guided patterns with long-range order and then remove one of the phases to achieve a mask for pattern transfer of the features. The etching impact on the ACE (Arkema-CEA) chemo-epitaxy flow has been studied and the etching steps have been optimized to eliminate self-assembly defects. In order to transfer the line patterns obtained through the block copolymer into the hard mask, we have developed a mixed wet and dry etching approach for a modified PS-b-PMMA high chi block copolymer presenting a pitch of 18 nm.

SCIENTIFIC COLLABORATIONS: ARKEMA (FR), Brewer Science Inc.(USA)

### Context and Challenges

For the sub-10 nm nodes, pattern scaling has slowed down due to conventional lithography limitations in terms of resolution, defectivity and cost. Our research proposes to introduce the Directed Self-Assembly (DSA) of block copolymers (BCPs) as a low-cost solution to obtain high-resolved and dense patterns. This approach is based on the self-assembly property of BCPs, which are capable of microphase separation, forming a dense array of ordered nanostructures with dimensions from 50 nm down to 5 nm.

### Main Results

We evaluated the impact of the etching steps involved in the ACE (Arkema-CEA) chemoepitaxy flow, namely regarding the adherence of the neutral layer. Following the flow optimization, we successfully demonstrated the chemoepitaxy of a PS-b-PMMA with 32 nm pitch without alignment defects on a 100 μm² surface (Figure 1) [1].

We then developed a mixed wet and dry etching approach to selectively remove the PMMA from a high-χ modified PS-b-PMMA with 18 nm pitch. With this approach, the pattern transfer of the PS lines into the SiO2 and silicon layers was validated (Figure 2). The results show that, for small and dense pitches, the main dry etching key challenges come from the trade-off between achieving high selectivity and avoiding bridge formation [2].

### Perspectives

Now that we have optimized the ACE flow and demonstrated an etching approach for the high- $\chi$  PS-b-PMMA on free surface, the next step will focus on adapting the flow to guide the 18-nm pitch high-x BCP into straight lines.

Figure 1: ACE flow applied to PS-b-PMMA.

Figure 2: Pattern transfer of PS lines

### RELATED PUBLICATIONS:

[1] M. G. Gusmão Cacho et al., Journal of Vacuum Science and Technology A, (39), 033004 (2021), https://doi.org/10.1116/6.0000850

[2] M. G. Gusmão Cacho et al., Microelectronic Engineering, (230) 111369 (2020), https://doi.org/10.1016/j.mee.2020.111369

## Sub-15 nm multilayer nanopillar patterning for hybrid SET/CMOS integration

### **RESEARCH TOPIC:**

Single-electron-transistor, nanopillars patterning, E-beam lithography, multilayer RIE, low-temperature plasma oxidation

### **AUTHORS:**

P. Brianceau, A. Gharbi, F. Laulagnet, G. Rademaker, J. V. Borany<sup>1</sup>, H.-J. Engelmann<sup>1</sup>, M. Rommel<sup>2</sup>, E. Amat<sup>3</sup>, M.-L. Pourteau

The Internet of Things (IoT) is a strongly growing market, with 20 billion connected devices expected in 2020. A critical constraint for those devices is to offer low power consumption. In this context, single-electron-transistors (SETs), consisting of a Si quantum dot lying between two tunnel junctions to neighboring drain and source Si regions, are gathering growing interest. For future industrialization, it is crucial to show a 200 mm CMOS-compatible fabrication of SETs working at room temperature. This is the goal of the IONS4SET European project in which LETI was involved in the last 4 years.

SCIENTIFIC COLLABORATIONS: 1 HZDR, Dresden (DE), 2 Fraunhofer-IISB, Erlangen (DE), 3 IMB-CNM, Bellaterra (ES)

### Context and Challenges

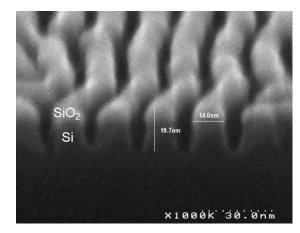

The SET physics is based on tunneling effect through a quantum dot between the source and drain of a gate-all-around nanopillar (NP) transistor, and typical Coulomb-blockade oscillations are observed on I-V plots. Those devices are functional at room temperatures and low voltages if the dimension of NP and quantum dot are in the nanometer range. From device simulations of various pillar geometries, we targeted the challenging patterning of NP of ~70 nm height and sub-15 nm diameter, with an embedded thin SiO<sub>2</sub> gate layer.

### Main Results

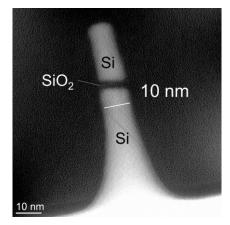

By combining electron-beam lithography with dry reactive ion etching, we have structured such NPs with a diameter down to 19 nm [1]. A resist trimming step enables to reduce the diameter, while the SOC/SiARC/resist tri-layer stack enhances etch selectivity. The CD uniformity is 2.5 nm, and NPs profile are straight. A sacrificial oxidation which consumes a fraction of the pillars surface Si, followed by HF removal of the oxide, further reduces the diameter. Low-temperature (<400°C) plasma oxidation using Hyperion® equipment from HQ-Dielectrics ensures the stability of the Si quantum dot in the oxide. NPs down to 10 nm diameter (Figure 1) have been reliably fabricated and contacted for further electrical testing (Figure 2) [2].

### Perspectives

A key future achievement is to integrate SETs in hybrid SET/FET devices.

Figure 1: TEM image of a NP after plasma oxidation

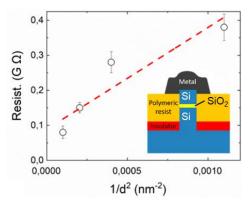

Figure 2: Resistance of contacted NP vs. diameter

- [1] M.-L.Pourteau et al., Micro and Nano Engineering, (9) 100074 (2020), <a href="https://doi.org/10.1016/j.mne.2020.100074">https://doi.org/10.1016/j.mne.2020.100074</a>, [2] E. Amat et al., Nanomaterials, 10(4), 716 (2020), <a href="https://doi.org/10.3390/nano10040716">https://doi.org/10.3390/nano10040716</a>

## Development of non-conventional chemistries for advanced CMOS spacer patterning

### **RESEARCH TOPIC:**

Dry and wet etch patterning of advanced logic devices

### **AUTHORS:**

O. Pollet, V. Ah-Leung, V. Bacquié, A. Tavernier, F. Boulard, N. Possémé

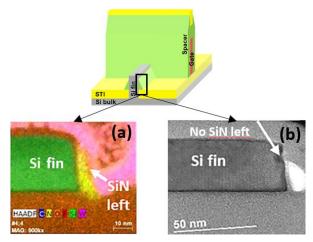

Silicon Nitride (SiN) spacer etching in 3D CMOS technologies has become a very challenging step to be able to complete the etching while preserving channel materials. The formation of parasitic spacers along fin sidewalls requires a lengthy overetch compared to conventional planar integrations. Thanks to SiCl<sub>4</sub> addition, we develop a cyclic strategy alternating selective passivation and nonselective etching. On nanowire-type patterned structures, it shows the full removal of the parasitic spacer while providing a silicon loss of less than 2 nm.

### Context and Challenges

The  $\mathrm{Si_3N_4}$  spacer forms the mask for source/drain implantation and protects the gate sidewalls for advanced CMOS transistor integration. Its etching is a critical step which requires selective etch stop and low damage on silicon. Moreover, in 3D CMOS technologies, gate stack and spacer materials must be etched away during patterning not only from horizontal planes like channel top or STI but also from channel sidewalls.

### Main Results

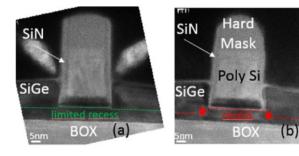

Thanks to the addition of  $SiCl_4$  to conventional  $CH_3F$  based chemistry, we show a selective etch stop and low damage on silicon by the formation of a  $SiO_xF_y$  passivation layer, which limits the transfer of the reactive layer into the silicon film. Application on the pattern revealed that this approach offers non-facetted  $Si_3N_4$  spacer, no foot formation, and 1 nm SiGe consumption [1]. For 3D CMOS integration, where parasitic spacer on fin sidewall should be removed, a cyclic sequence alternating  $SiCl_4$  steps with nonselective  $CHF_3$  steps is developed and validated. When applied to nanowire patterned structures, this process demonstrates to induce less than 2 nm of silicon loss despite the long overetch used to thoroughly eliminate parasitic spacers on fin sidewalls [2].

### **Perspectives**

Further developments are ongoing to enhance SiCl<sub>4</sub>-containing process performances on patterned structures and make them fulfill specifications for spacer etching in 3D CMOS integration.

Figure 1: Etching with (a) or without (b) SiCl<sub>4</sub> addition

Figure 2: Continuous (a) vs. cyclic (b) approach

- [1] N. Posseme, et al., J. Vac. Sci. Technol. A 38, 033004 (2020) https://doi.org/10.1116/1.5145158

- [2] O. Pollet, et al., J. Vac. Sci. Technol. A 38, 063007 (2020) https://doi.org/10.1116/6.0000584

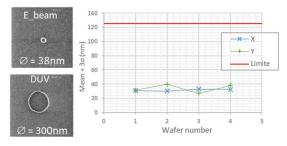

## Hybrid E-beam lithography capabilities for a large field of nanodevice applications

### **RESEARCH TOPIC:**

hybrid lithography, E-beam, DUV, resists, shape-beam tool, advanced devices

### **AUTHORS:**

F. Laulagnet, M. Cannac, A. Gharbi, J.A. Dallery<sup>1</sup>, C. Charpin-Nicolle, Marceline Bonvalot<sup>2</sup>, S. Landis, P. Sixt, I. Servin

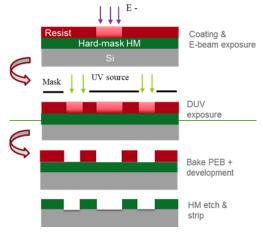

Maskless lithography is versatile and a cost-effective patterning approach, well suited for demonstrators of nanodevice fabrication and covering a large field of applications (Photonic, Displays/LED, Memories, FDSOI, quantum computing, MEMS or RF). The hybrid lithography concept allows to reduce significantly writing time by coupling high-resolution of Electron Beam Direct Write (EBDW) lithography and high-throughput of a mask-based DUV lithography. This approach involves two consecutive exposures using a unique resist, unlike complex "mixand-match" multiple patterning strategies.

CEA-Leti demonstrate high-resolution capability down to 30 nm, while matching the whole process to two consecutive exposures and preserving alignment performances.

SCIENTIFIC COLLABORATIONS: 1Vistec Electron Beam GmbH, Jena (DE), 2CNRS-LTM, Grenoble (FR)

### Context and Challenges

The hybrid lithography approach involves two consecutive exposures using a unique resist, which is an elegant process without additional etch step. The high-resolved patterns are reserved to E-beam writing whereas non-critical patterns are exposed on DUV optical scanner. The main advantages are writing time gain, design layout flexibility and high resolution but it requires a compatible resist for both exposures and manage delay time constraint and alignment matching between the two lithography tools [1].

### Main Results

Hybrid lithography approach is illustrated by the example of memory cells for OXRAM devices [2]. The patterned cells of 30 nm are printed with E-beam and the less aggressive patterns (> 300nm) are exposed on a DUV scanner using a unique negative chemically amplified resist (CAR) with thickness of 70 nm. The CD uniformity and alignment (OVL) are within specifications

The interest of hybrid lithography was fully demonstrated in terms of gain in throughput, high-resolution by matching the single resist process to both E-beam & DUV lithography. To extend hybrid flow to novel resist platforms with DUV 193 nm, alternative solutions to conventional CAR resists show promising results in terms of sensitivity, resolution, LWR and stacking compatibility.

### Perspectives

This new process capability will also strengthen our ability to quickly evaluate new high-resolution designs developed for quantum computing and IA, before moving to immersion 193 nm optical lithography platform which would require a complex and expensive mask set.

Figure 1: Hybrid lithography concept

Figure 2: CD-SEM patterns and OVL Mean + 3σ between E-beam and DUV level

- [1] I. Servin et al., Proc. SPIE 11518, Photomask Technology, (2020), <a href="https://doi.org/10.1117/12.2572868">https://doi.org/10.1117/12.2572868</a></a>

[2] C. Charpin-Nicolle et al., Microelectronic Engineering, (221), 111194, (2020), <a href="https://dx.doi.org/10.1016/j.mee.2019.111194">https://dx.doi.org/10.1016/j.mee.2019.111194</a>

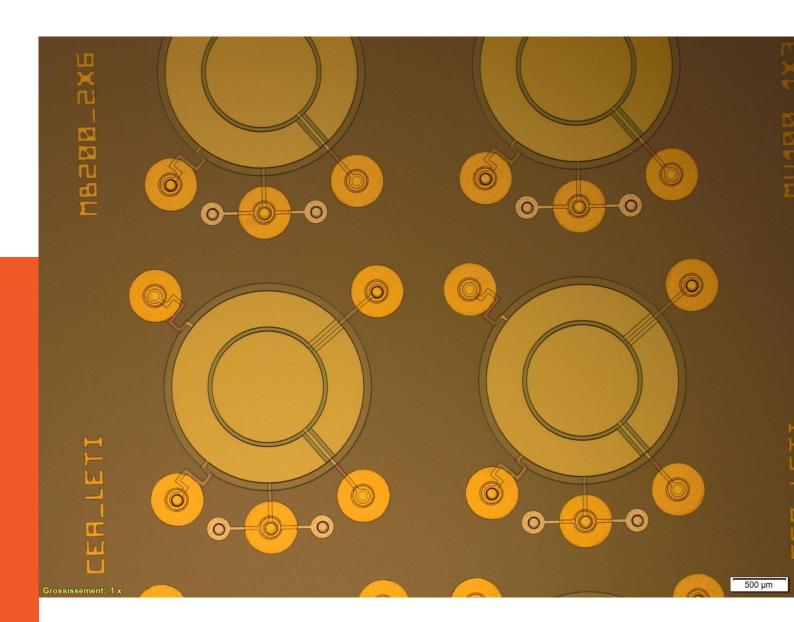

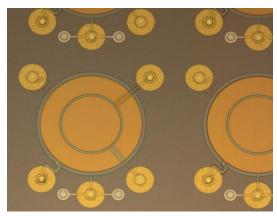

## **Piezoelectric Membrane Ultrasonic Transducer**

© CEA-Leti

04

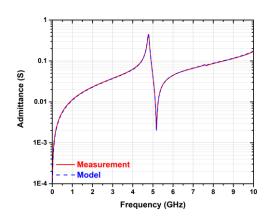

## MEMS, NEMS & RF COMPONENTS

- AIN-based bimorph piezoelectric micromachined ultrasound transducers for air-borne applications

- Potentialities of single-crystal LiNbO<sub>3</sub> and LiTaO<sub>3</sub> film bulk acoustic resonators for high-frequency filters

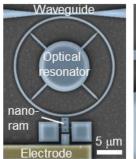

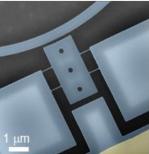

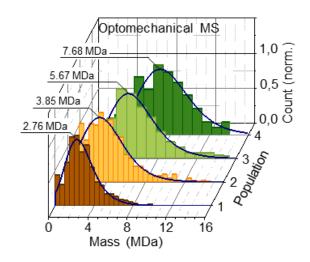

- Optomechanical mass sensing

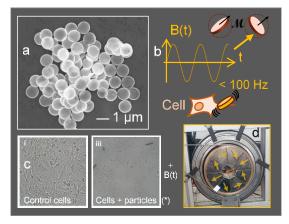

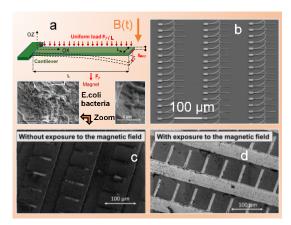

- Magnetically actuated nanostructures for biotechnologies: examples of cancer cells destruction and inhibition of bacterial biofilms formation

## AlN-based bimorph piezoelectric micromachined ultrasound transducers for air-borne applications

### **RESEARCH TOPIC:**

Piezoelectric MEMS, Micromachined Ultrasonic Transducer, Time-of-Flight measurement

### **AUTHORS:**

J.C. Bastien, J. Jung, F. Blard, F. Gardien, K. Benedetto, **B. Fain**

In the last years, piezoelectric micromachined ultrasound transducers (pMUT) have raised a great interest for various applications such as obstacle localization, gesture recognition, fingerprint sensing and advanced biomedical applications. Compared to conventional bulk transducer, pMUT are much easier to miniaturize and co-integrate with electronics, what offers important possibilities. CEA-Leti has developed bimorph AIN-based pMUTs, a particular structure that presents good properties for both emission and reception, and are particularly relevant for air-borne pulse-echo measurements.

### Context and Challenges

pMUT transducers are both sensors and actuators. Depending on the application, piezoelectric material may be chosen to optimize emission or reception properties. A challenge is to overcome the emission / reception trade-off using a specific bimorph pMUT architecture.

### Main Results

We developed an AIN-based bimorph pMUT architecture for air-borne pulse-echo measurements around 100 kHz. As presented in [1], this structure includes four electrode pairs that may be combined to enhance the drive sensitivity. The low dielectric permittivity of AIN and the four channels should also ensure good receive sensitivity and low noise at the electronics stage.

The acoustic characterization of pMUTs confirms the potential of such structure for emission and reception. The figure below presents the pressure emitted by a single membrane excited by a 1V sinusoidal electric actuation at 103 kHz, which is of 70 dB at 50 cm. For reception, the pMUT membrane is used to measure the pressure of a commercial emitter calibrated beforehand. A single membrane may measure a pressure as low as a few mPa, thanks to a dedicated discrete electronics

### **Perspectives**