## HANOI "Whiteboard" Flow The Seed For 2.5D-IC Implementation

## Anna Fontanelli, Founder & CEO

## The Problem Almost Nothing Exists, the Blackboard Is... White

- The processor (xPU) is in the flux

- The memories selection is still ongoing

- The silicon interposer(s) do(es) not exist yes, there may be more than one !

- The package selection is a far future concern

- Yet, some "drawing" is critical to plan ahead

- Complexity prevents "napkin and pencil" approaches

- Thousands of signals, microbumps, TSV, C4, design-rules,...

- HANOI does provide a "whiteboard" flow to the rescue

- What exists can be imported, what doesn't exist can be created from scratch

## Z HANOI "Whiteboard" Flow The Seed for 2.5D-IC Physical Implementation

## Incremental Optimization

Import from Physical Implementation

Components Update

Logical, Physical

Silicon Interposer Update

Incremental I/O Planning

Incremental Optimization

Incremental Signal Assignment

Export to Physical Implementation

## HANOI "Whiteboard" Flow The Seed for IC Compiler Physical Implementation

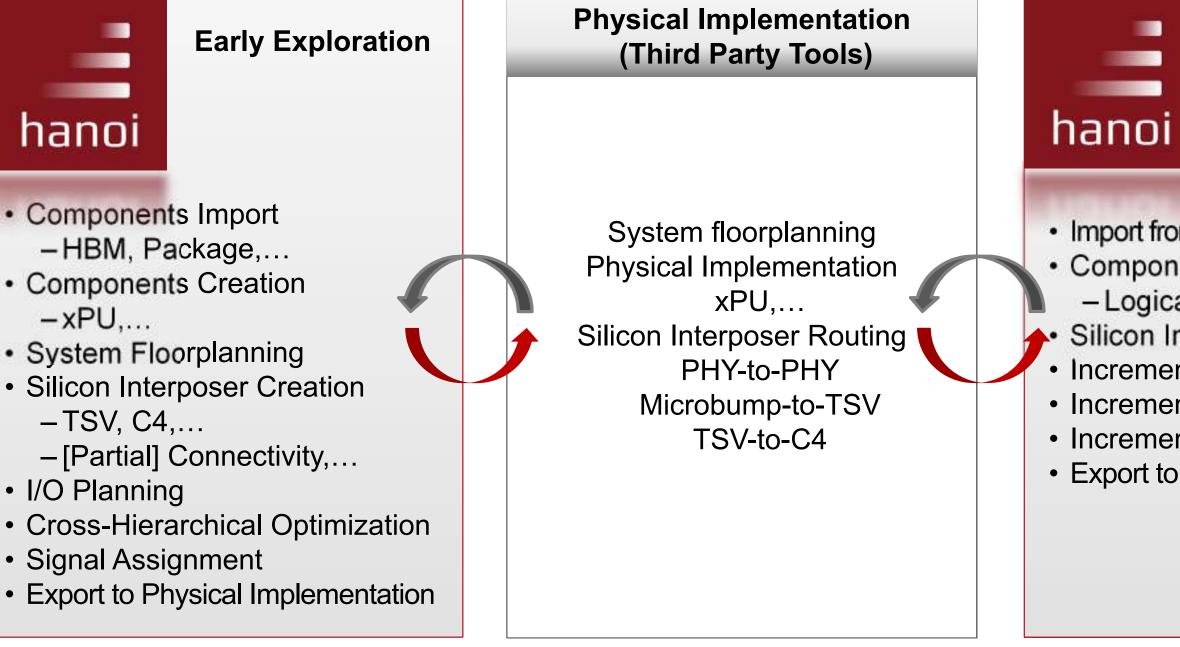

## Early Exploration

### Hanoi

hanoi

- **Components Import**

- -HBM, Package,...

- Components Creation -xPU,...

- System Floorplanning

- Silicon Interposer Creation -TSV, C4,...

- [Partial] Connectivity,...

- I/O Planning

- Cross-Hierarchical Optimization

- Signal Assignment

- Export to Physical Implementation

## **SYNOPSYS**<sup>®</sup> Physical Implementation

## IC Compiler & Custom Compiler

- System floorplanning

- Physical Implementation

- -xPU....

## Hanoi

- Import from Physical Implementation

- Components Update -Logical, Physical

- Silicon Interposer Update

- Silicon Interposer Routing -PHY-to-PHY

- Incremental I/O Planning

- Incremental Optimization

### **Incremental Optimization** hanoi

## – Microbump-to-TSV-to-C4

## Incremental Signal Assignment • Export to Physical Implementation

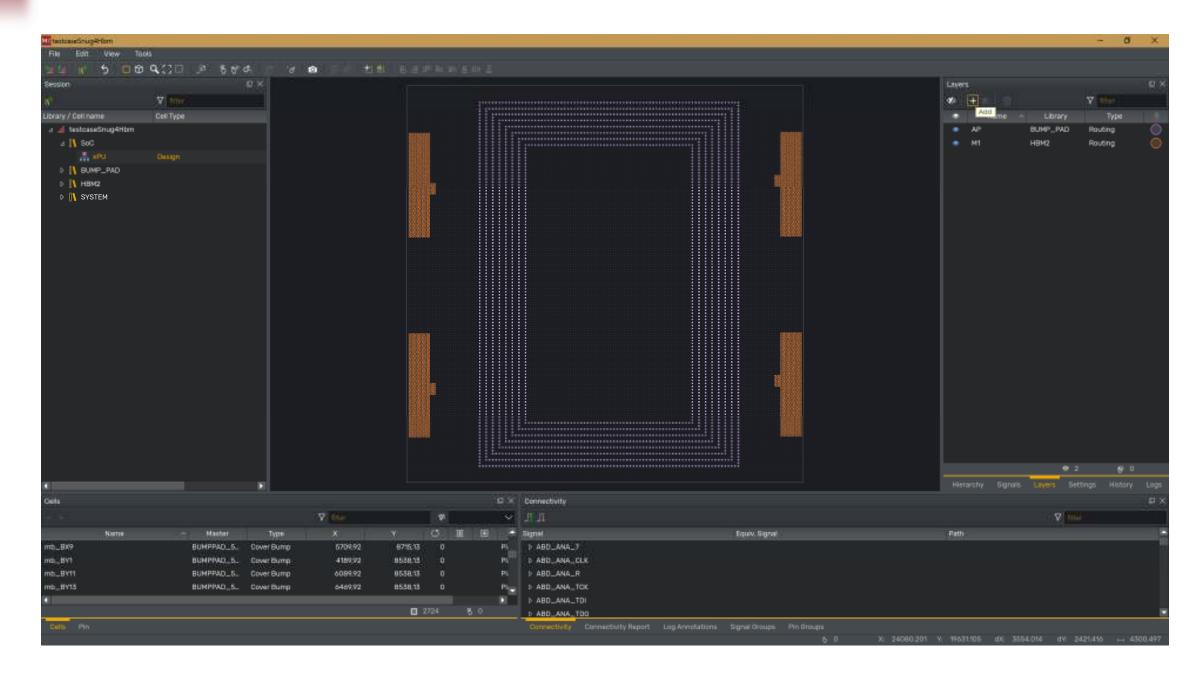

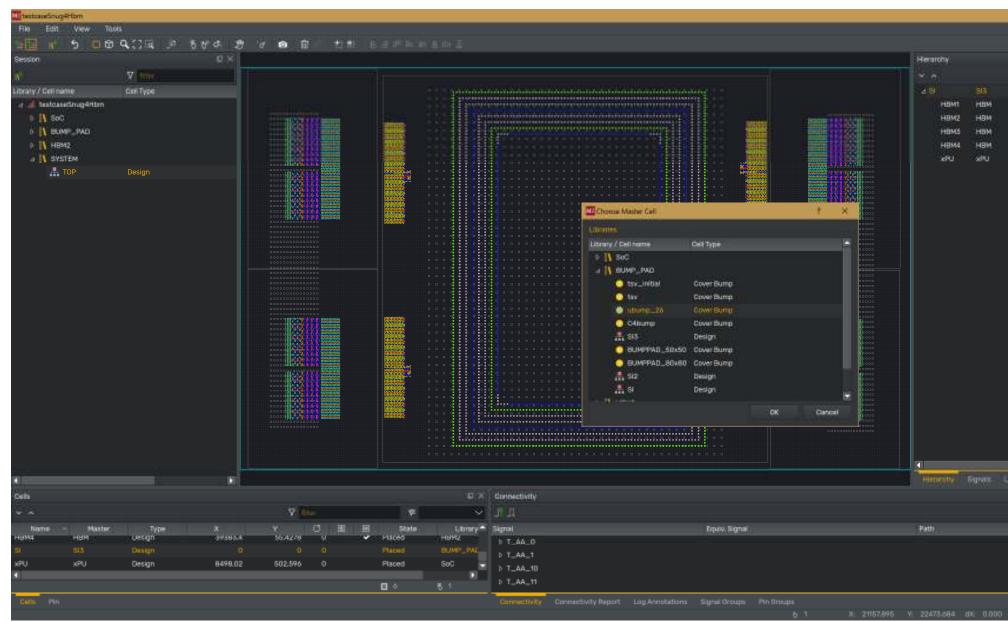

## MZ HBM Component Import Excel/AIF Format Including Signal Assignment

| 177 testcaseSnug4Hbm            |                      |              |           |                 |                       |                                                                           |                              |

|---------------------------------|----------------------|--------------|-----------|-----------------|-----------------------|---------------------------------------------------------------------------|------------------------------|

| File Edit View To               |                      |              |           |                 |                       |                                                                           |                              |

|                                 | ୍ୟା ଅପ୍ରାର୍ମ ସ<br>ଏବ | ਰ 🖸          |           |                 |                       |                                                                           | Circle 10                    |

| Session                         |                      |              |           |                 |                       |                                                                           | Signals                      |

| W                               | <b>▼</b> filter      |              |           |                 |                       |                                                                           |                              |

| ibrary / Cell name              | Cell Type            | 4            |           |                 |                       |                                                                           | Name                         |

| ∠ _= testcaseSnug4Hbm ▷ []\ SoC |                      |              |           |                 |                       |                                                                           | RSVD5     SELECTWIR          |

| D N BUMP_PAD                    |                      |              |           |                 |                       |                                                                           | SHIFTWR                      |

| ⊿ <b>[] HBM2</b>                |                      |              |           |                 |                       |                                                                           | Ф ТЕМРО                      |

| . НВМ                           | Design               |              |           |                 |                       | 1333 (1) (1) (1) (1) (1) (1) (1) (1) (1) (1)                              | темр1                        |

| 👫 PHY2                          | Design               |              |           |                 |                       |                                                                           | ∞ TEMP2                      |

| D 🚺 SYSTEM                      |                      |              |           |                 |                       |                                                                           | UPDATEWR                     |

|                                 |                      |              |           |                 |                       |                                                                           | VDDC                         |

|                                 |                      |              |           |                 |                       |                                                                           | VDDQ                         |

|                                 |                      |              |           |                 |                       |                                                                           | VPP                          |

|                                 |                      |              |           |                 |                       |                                                                           | Ø VSS                        |

|                                 |                      |              |           |                 |                       |                                                                           |                              |

|                                 |                      |              |           |                 |                       |                                                                           | WDQSa0_t<br>WDQSa1_c         |

|                                 |                      |              |           |                 |                       |                                                                           | WDQSa1_t                     |

|                                 |                      |              |           |                 |                       |                                                                           | WD0Sa2_c                     |

|                                 |                      |              |           |                 |                       |                                                                           | ⊘ WD0Sa2_t                   |

|                                 |                      |              |           |                 |                       |                                                                           | WDQSa3_c                     |

|                                 |                      |              |           |                 |                       |                                                                           | <pre>wDQSa3_t</pre>          |

|                                 |                      |              |           |                 |                       |                                                                           | <pre> WDQSb0_c </pre>        |

|                                 |                      |              |           |                 |                       |                                                                           | WDQSb0_t     WDQSb0_t        |

|                                 |                      |              |           |                 |                       |                                                                           | ≪ WDQSb1_c                   |

|                                 |                      |              |           |                 |                       |                                                                           | WDQSb1_t                     |

|                                 |                      |              |           |                 |                       |                                                                           | Hierarchy Signals            |

|                                 |                      | <b>T</b> .S  |           |                 | ſ                     | × Pin Groups                                                              |                              |

|                                 |                      |              |           | <b>∇</b> filter |                       |                                                                           |                              |

|                                 | Path                 | ∧ Туре       | Cell Type | Signal name     | 0 Å                   |                                                                           |                              |

| ERRa                            |                      | Input Output | Design    | AERRa           | ~                     |                                                                           |                              |

| ERRb                            |                      | Input Output | Design    | AERRb           | ~                     |                                                                           |                              |

| ERRC                            |                      | Input Output | Design    | AERRC           | ~                     |                                                                           |                              |

| ERRd                            |                      | Input Output | Design    | AERRd           | ~                     |                                                                           |                              |

| ERRe                            |                      | Input Output | Design    | AERRe           | <ul> <li>*</li> </ul> |                                                                           |                              |

| ERRf                            |                      | Input Output | Design    | AERRF           | ~                     |                                                                           |                              |

| ERRg                            |                      | Input Output | Design    | AERRg           | <b>*</b>              |                                                                           |                              |

|                                 |                      |              |           | ♦ 4942          | 80                    |                                                                           |                              |

| Cells Pin                       |                      |              |           |                 |                       | Connectivity Connectivity Report Log Annotations Signal Groups Pin Groups |                              |

| Ready                           |                      |              |           |                 |                       | 60 X: 1                                                                   | 0064.895 Y: 6491.435 dX: 0.0 |

|       |         |      | 100   |      | 100 | 2  |

|-------|---------|------|-------|------|-----|----|

|       |         | =    | Ĺ     | 2    | ×   | i. |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      | ø   |    |

|       | 7 111   |      |       |      |     |    |

| ۲     |         | Туре |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

| ~     | Signal  |      |       | 8    |     |    |

|       | Signal  |      |       |      | Ň   |    |

| -     | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

|       | Signal  |      |       |      |     |    |

| ayers | Setting |      | Histo |      | Log |    |

|       |         |      |       |      | D   |    |

|       |         |      |       |      |     |    |

| V     |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       |         |      |       |      |     |    |

|       | v. 0.00 |      |       | 0.00 | 10  |    |

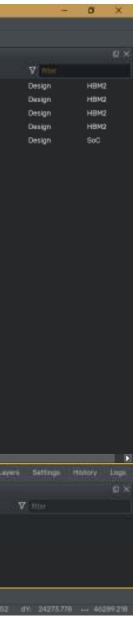

## MZ Processor Component Creation Whiteboard Flow in HANOI

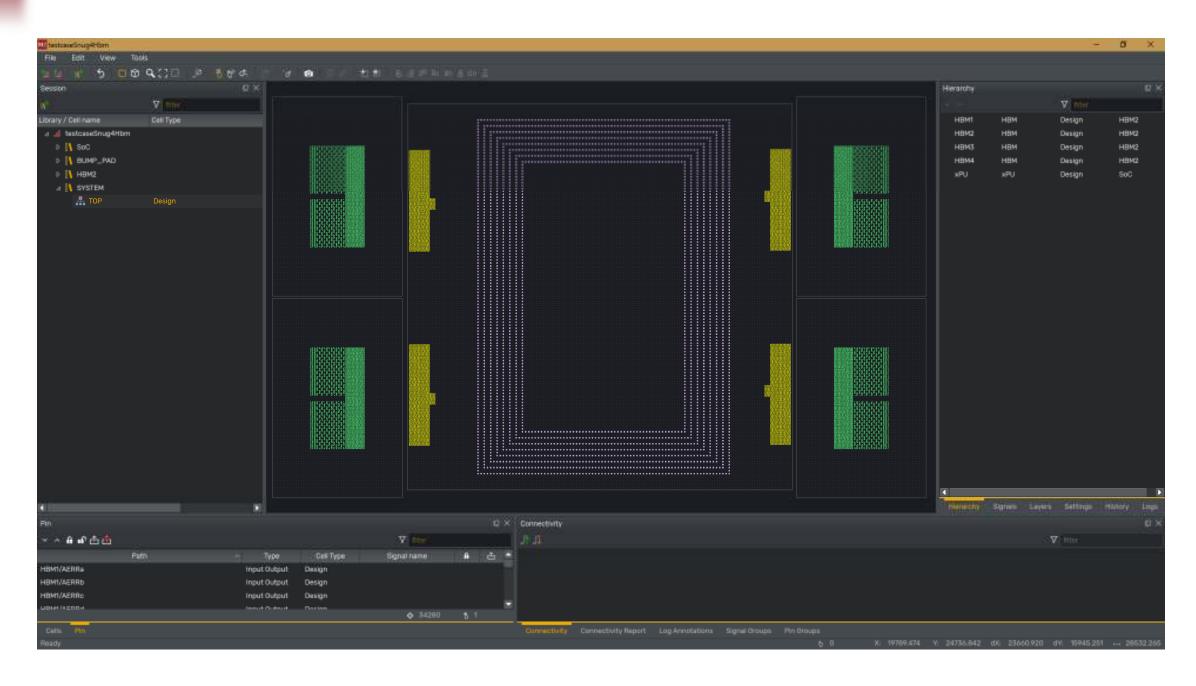

# **MZ System Composition & Floorplanning** *Alignment Functionalities Facilitate Placement*

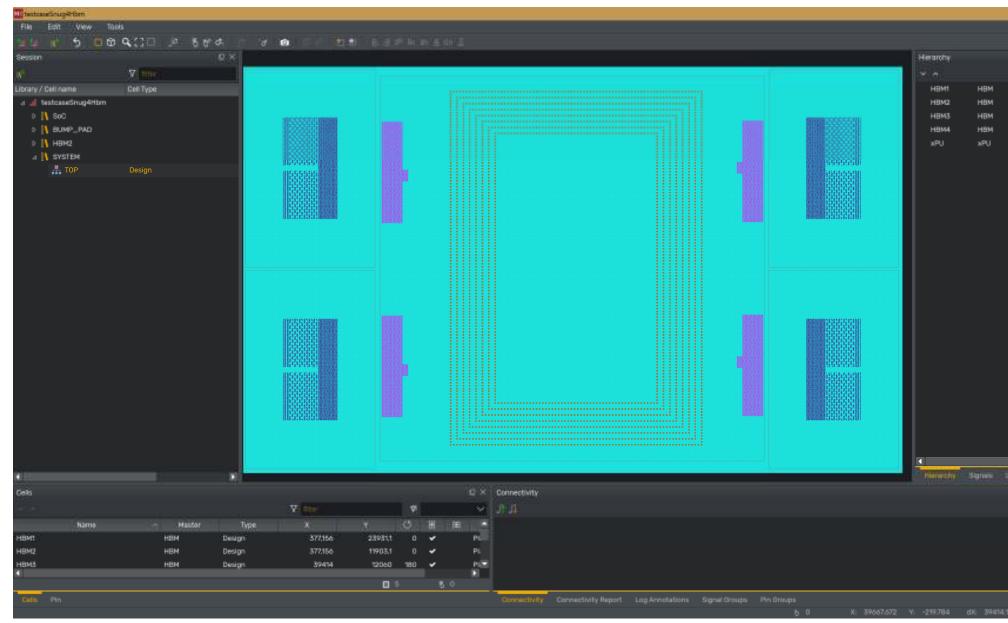

## **MZ** Silicon Interposer Creation Boundary Definition

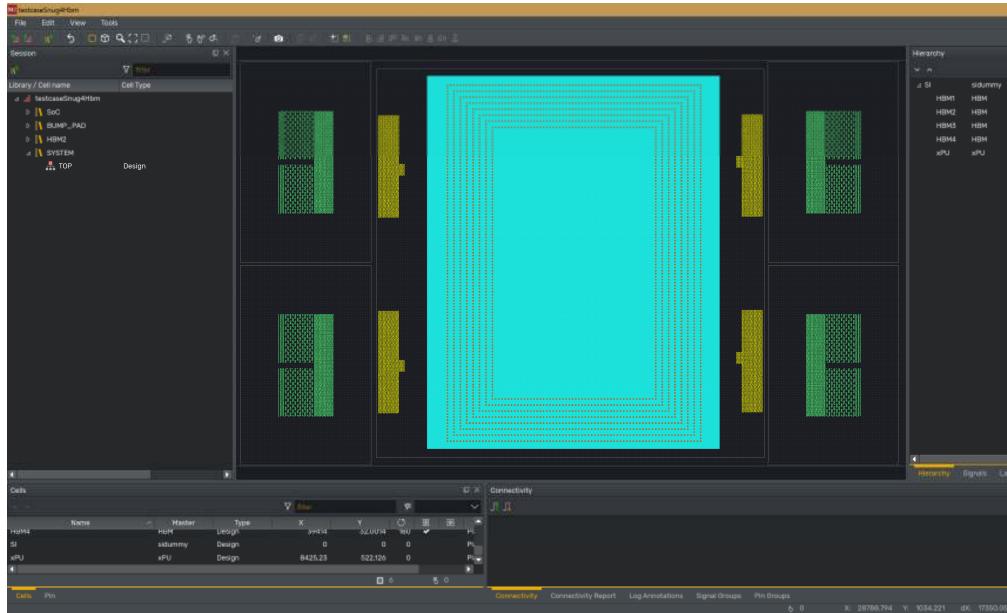

# **MZ Silicon Interposer Creation** *Multiple Bumping Areas Creation*

|       |         | -                 | ø         | ×    |

|-------|---------|-------------------|-----------|------|

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       | V) mire |                   |           |      |

|       | Design  |                   | BUMP_     | .PAD |

|       | Design  |                   | HBM2      |      |

|       | besign  |                   | SeC       |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       | Betting | = <del>1</del> 00 | tery ( ). | Lope |

|       |         |                   |           |      |

| V     |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

|       |         |                   |           |      |

| 52 dY | 22086   | 5.219 H           | → 2808    | 2008 |

## MZ Silicon Interposer Bumping Grid Definition by Number/Pitch/...

|   |         | - | ø     | ×   |

|---|---------|---|-------|-----|

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   | V min   |   |       |     |

|   | Design  |   | BUMP. | PAD |

|   | Design  |   | HBM2  |     |

|   | Design  |   | SoC   |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   | Getting |   |       |     |

|   |         |   |       |     |

| 7 |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   |         |   |       |     |

|   | 19194   |   |       |     |

|   |         |   |       |     |

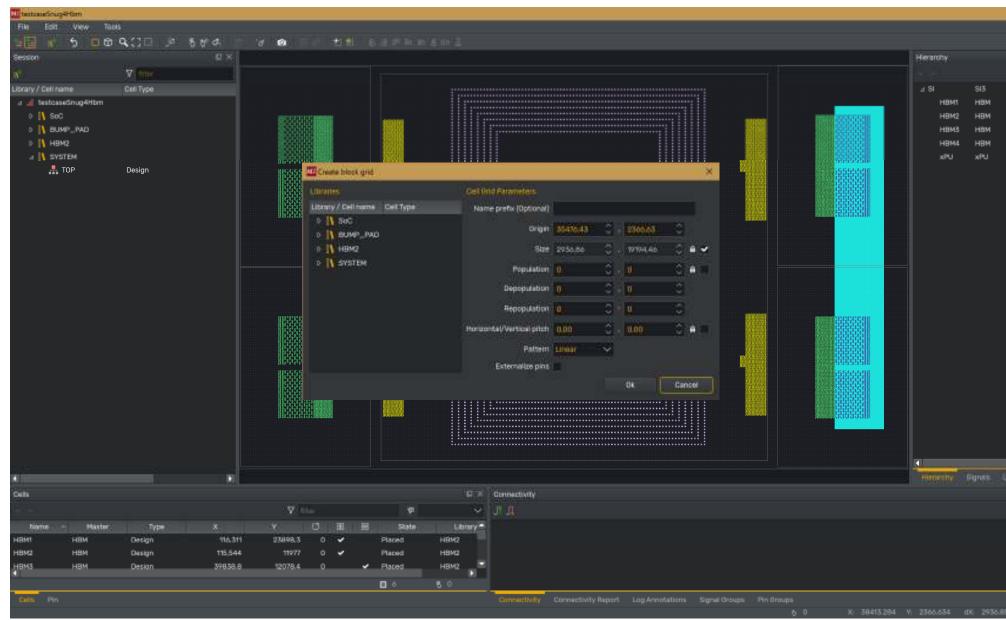

## MZ System Connectivity

Import from Verilog/csv and Global Signals Highlight

## MZ

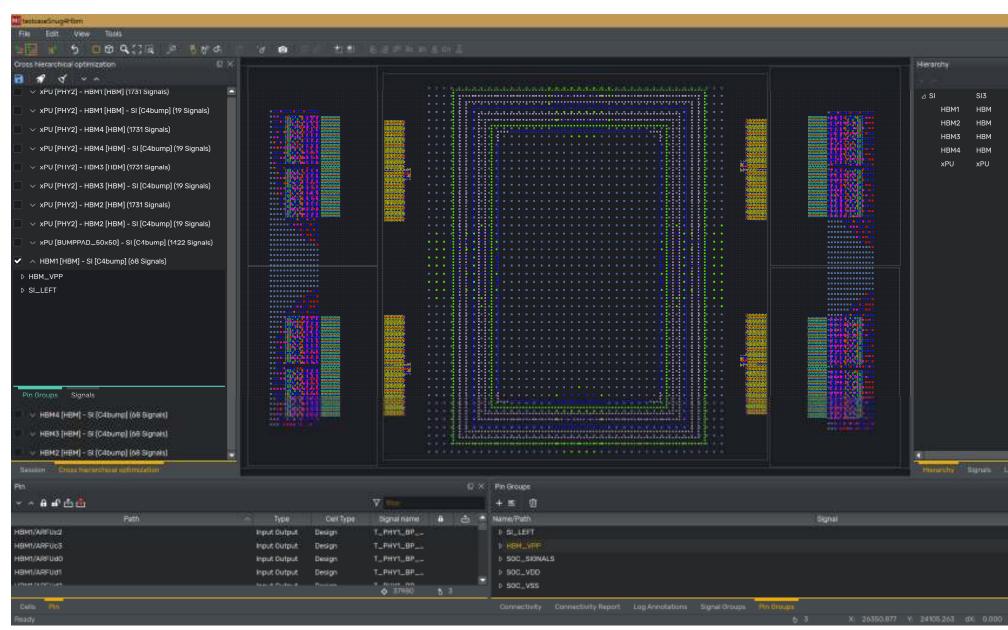

## **Cross Hierarchical Optimization** Signal & Pin Groups Driven: What & Where Approach

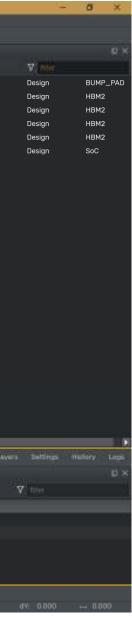

# **MZ Time Machine Functionality** *Report Generated on «Tagged» Versions*

|              | - 0 >              | Č.   |

|--------------|--------------------|------|

|              |                    |      |

|              |                    |      |

|              |                    | ×    |

|              |                    |      |

| varialura -  | 19/5/2017 12:63:59 |      |

| 7            | 19/5/2017 12:53:53 |      |

|              | 19/5/2017 12:53:48 |      |

| ad .         | 19/5/2017 12:53:28 |      |

| jed.         | 19/5/2017 12:53:24 |      |

|              | 1016/2017/32/55/22 |      |

| jed          | 19/5/2017 12:53:19 |      |

|              | 19/5/2017 12:52:17 |      |

|              | 19/5/2017 12:52:11 |      |

|              | 19/5/2017 12:52:03 |      |

|              | 19/5/2017 12:51:48 |      |

|              | 19/5/2017 12:51:38 |      |

| anged        | 19/5/2017 12:51:29 |      |

|              | 19/5/2017 12:51:29 |      |

|              | 19/5/2017 12:51:23 |      |

| ctable       | 19/5/2017 12:50:33 |      |

| SV)          | 19/5/2017 12:50:15 |      |

|              | 19/5/2017 12:46:49 |      |

|              | 19/5/2017 12:46:35 |      |

|              | 19/5/2017 12:46:00 |      |

|              | 19/5/2017 12:44:56 |      |

| BUMPPAD      | 19/5/2017 12:43:57 |      |

| jed          | 19/5/2017 12:42:19 | I    |

| jed          | 19/5/2017 12:42:03 |      |

|              | 19/5/2017 12:41:27 |      |

|              | 19/5/2017 12:41:27 |      |

|              | 19/5/2017 12:41:24 |      |

|              | 19/5/2017 12:41:24 |      |

|              | 19/5/2017 12-41-18 |      |

| Avers Bettin | ge History Los     | pii. |

|              |                    | ×    |

|              |                    | -    |

|              |                    |      |

|              |                    |      |

|              |                    |      |

|              |                    |      |

|              |                    |      |

|              |                    |      |

|              |                    |      |

| dY: 0.00     | 000.0 ⊶ 0.000      |      |

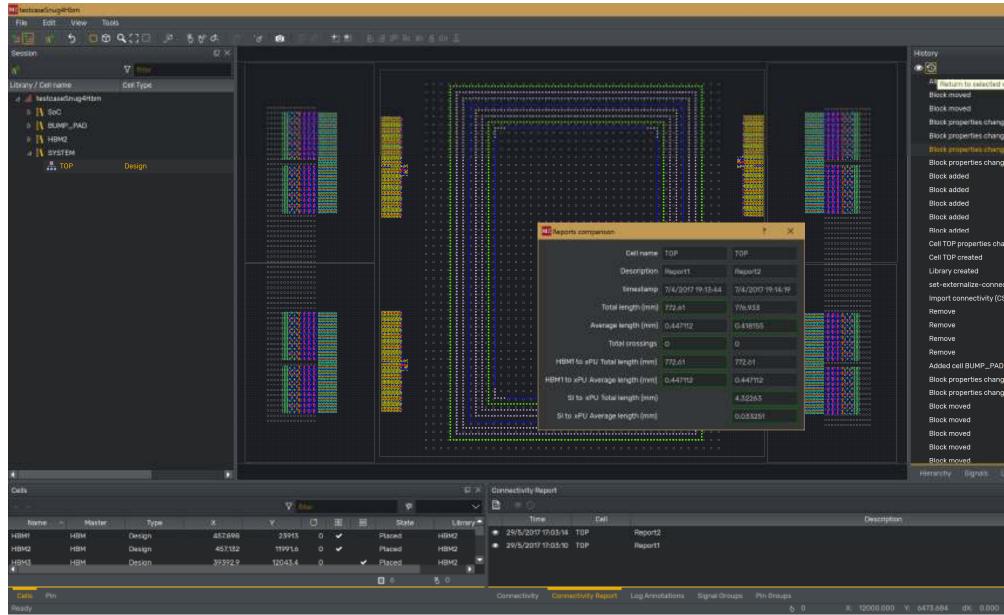

### Fly-Lines Toggle For PHY-To-PHY Signals,... MZ Show & Hide Approach

| 102 testcaseC                                                 |                                                 |                                                  |

|---------------------------------------------------------------|-------------------------------------------------|--------------------------------------------------|

| Eile Edit Tools Help                                          |                                                 |                                                  |

| 995 00 0 Q Q Q R 8 8 8 4 4                                    | <u>ජී වී 🖗 🔿</u>                                |                                                  |

| Ottimizzazione cross gerarchica 🛛 🗴 🖉 🗙                       |                                                 | Livelli                                          |

| B # 4 * ^                                                     |                                                 |                                                  |

| HBM2 [Cover Bump] - SI [Cover Bump] (58)                      |                                                 | 🔹 Name 4                                         |

| NPU [Cover Bump] - HBM2 [Cover Bump] (1728)                   |                                                 | <sup>.</sup> <sup>2</sup>                        |

| ♥ NPU [Cover Bump] - HBM2 [Cover Bump] - SI [Cover Bump] (46) |                                                 |                                                  |

| ♥ NPU [Cover Bump] - SI [Cover Bump] (1422)                   |                                                 | CBV                                              |

| A NPU [Cover Bump] - HBM1 [Cover Bump] (1728)                 |                                                 |                                                  |

|                                                               |                                                 | 🗰 🗰 🗰 🗰 🗰 🗰 🗰 🗰 🗰 🖉 CHOpt layer : HBM1 - Si      |

|                                                               |                                                 | CHOpt layer : NPU - HB.                          |

|                                                               |                                                 | LABEL                                            |

|                                                               |                                                 |                                                  |

|                                                               |                                                 |                                                  |

|                                                               |                                                 | • PINTEXT                                        |

|                                                               |                                                 | RUBBER_BAND                                      |

| And                       |                                                 | Gerarchia Segnali Livel                          |

|                                                               |                                                 |                                                  |

| NPU [Cover Bump] - HBM1 [Cover Bump] - SI [Cover Bump] (46)   |                                                 | Scene rendering                                  |

| ♥ HBM1 [Cover Bump] - SI [Cover Bump] (68)                    |                                                 | Scene rendering                                  |

|                                                               |                                                 |                                                  |

|                                                               |                                                 | Obsolete groups deletion: 0.09<br>Scene building |

|                                                               |                                                 | Calculated bounding box: 0, 0, 0                 |

|                                                               |                                                 | Scene cleanup                                    |

|                                                               |                                                 | Building scene                                   |

|                                                               |                                                 | Task 'Cross Hierarchical Optimiz                 |

|                                                               |                                                 | Operation: 'crossHierarchicalOp                  |

|                                                               |                                                 | total elapsed: 11892ms<br>concurrent : paths 0   |

| Sessione Ottimizzazione cross gerarchica                      |                                                 | suurballe runtime: Oms                           |

| lins                                                          | 🛛 🗶 Gruppi di Pin                               |                                                  |

|                                                               | ▼<br>▼                                          |                                                  |

| Name 🗢 Type Cell Type Signal Name                             | Group (Pin page                                 |                                                  |

| 4right_AJ24.IN Input Output Cover Bump                        | SI D SI_LEFT                                    |                                                  |

| 4right_AJ25.IN Input Output Cover Bump                        | SI DEBUT DE | INEL                                             |

| c4right_AJ26.IN Input Output Cover Bump                       | 51 • PHY2_VDD0<br>- • PHY1_VS5                  |                                                  |

|                                                               | -                                               | 15:                                              |

| Celle Pins                                                    | Connettività Routes                             | Annotazioni Gruppi di Pin                        |

| Pronto                                                        |                                                 | 6 3 X: 14136.709 Y: 17971.196 dX: 2.633          |

## MZ ...And Global Signals Show & Hide Approach

|       |         | -    | ٥       |          | ×  |   |

|-------|---------|------|---------|----------|----|---|

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          | ø  |   |

|       | 7 111   |      |         |          |    |   |

| ۲     |         | Туре |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

|       | Signal  |      |         |          |    |   |

| ~     | Signal  |      |         |          |    |   |

| ~     | Signal  |      |         |          |    |   |

| ~     | Signal  |      |         |          | )  |   |

| ~     | Signal  |      |         |          |    |   |

| ayers | Setting | gs   | History | $\sim 1$ | og | s |

|       |         |      |         |          | ø  | × |

| V     |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

|       |         |      |         |          |    |   |

| d)    | : 0.00  |      | test (  | 0.000    |    |   |

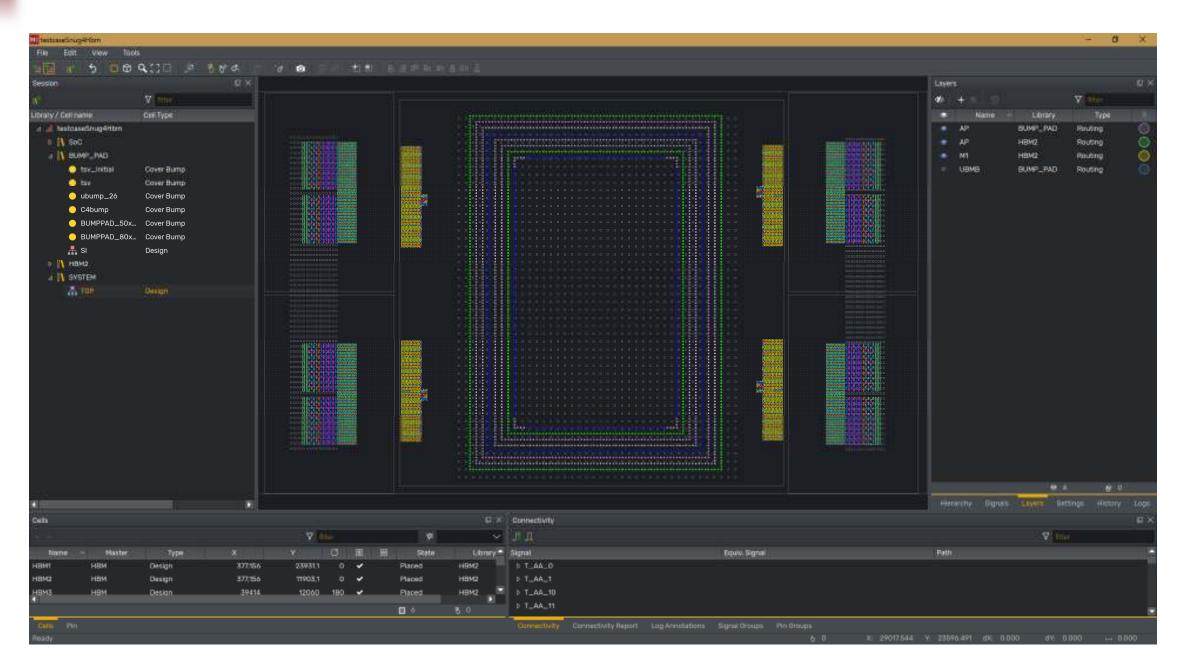

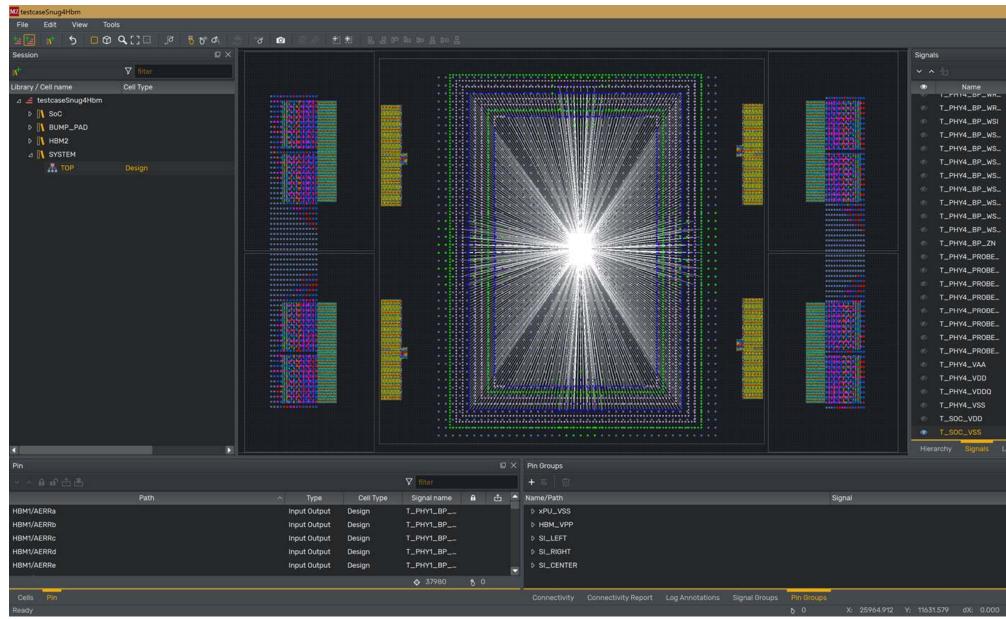

# **Mirroring of Microbumps on Silicon Interposer**

|      |            | -   | ø      | ×     |

|------|------------|-----|--------|-------|

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      | V min      |     |        |       |

|      | Jestan).   |     | COMP.  | PAD   |

| 10   | Resign     |     | HBM2   |       |

|      | Design     |     | HBM2   |       |

|      | Design     |     | HBM2   |       |

|      | Design     |     | HBMZ   |       |

| 1    | Design     |     | SeC    |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      | the second |     |        | 1.000 |

|      |            |     |        | 100   |

|      |            |     |        |       |

| - V  |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        | 1     |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      |            |     |        |       |

|      | 0.000      |     | → 0.00 |       |

| - 01 | 0.000      | · · | - 0.00 |       |

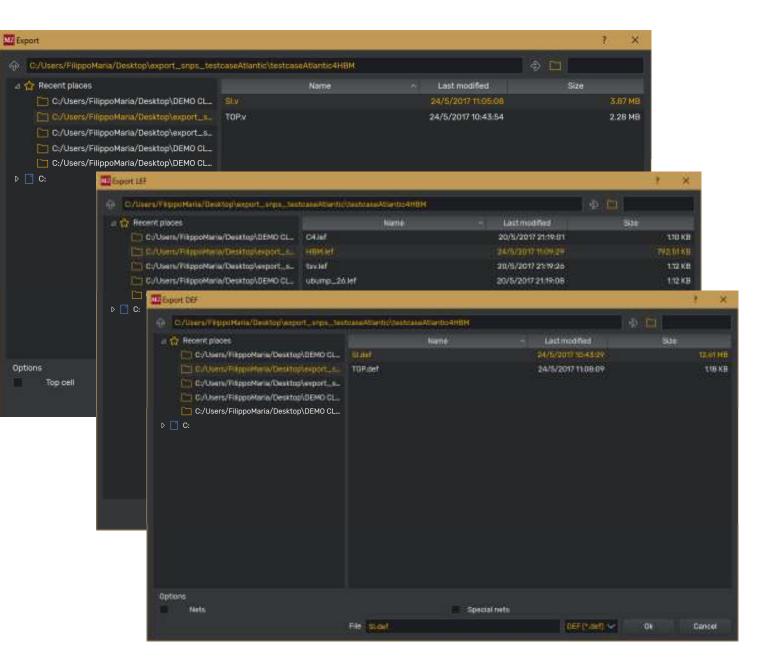

## MZ Export To IC Compiler & Custom Compiler Regular vs. High-Speed Signals Routing Tools

- Silicon Interposer Routing

- DEF + Verilog

- Silicon Interposer Component

- LEFs

- Bumps (C4 e landing pad) and TSV

- High Speed Signals Routing

- DEF + Verilog

- TOP Level

- LEFs

- HBM & xPU

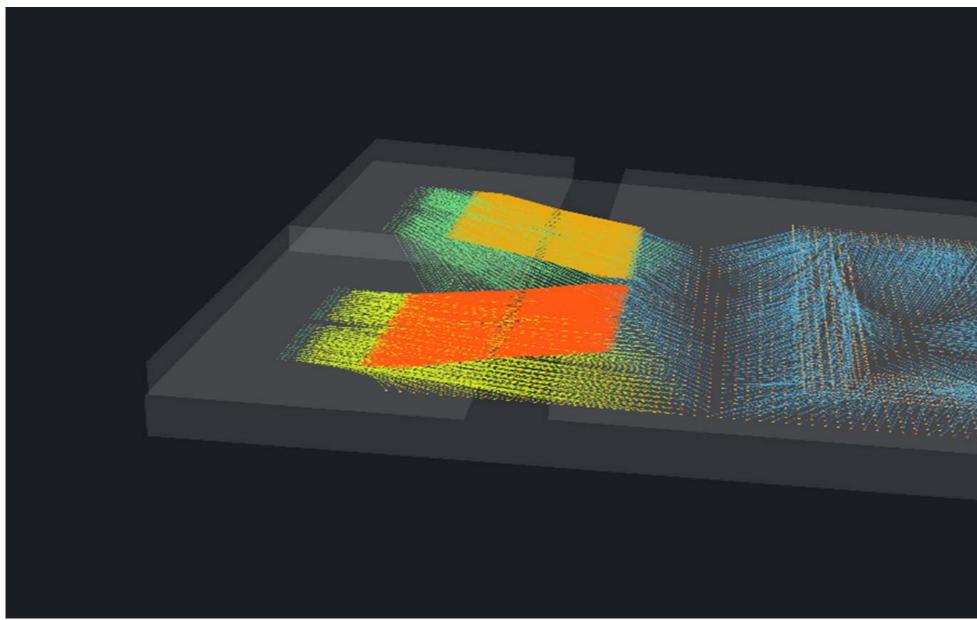

# **MZ System 3D View** *Detail of HBM-to-xPU-to-SI Fly-Line Connections*

- HANOI does provide a "whiteboard" flow to the rescue

- What exists can be imported, what doesn't exist can be created from scratch

- Many different configurations can be explored in a matter of hours

- SI(s) interactively generated according to floorplan & design rules

- Cross-hierarchical optimization enables overall best path-finding

- Validated Roundtrip with IC Compiler

- Industry only solution for package-silicon interposer-die co-design - Common environment to represent <u>all</u> the levels of a 2.5D-IC design

- There is much more to HANOI than 2.5D-IC !

# Thanks!