## leti ceatech

#### 5G\_GAN2 ECSEL PROJECT: 200mm CMOS COMPATIBLE GaN/Si HEMT FOR KA BAND POWER AMPLIFIER

#### CEA LETI| Hervé RIBOT | 26/06/2018

#### **KEY OBJECTIVES**

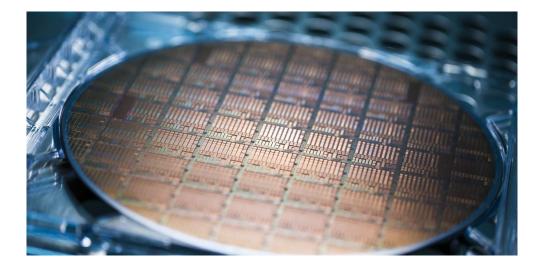

#### Leveraging LETI platform on 200mm N<sub>on</sub> power transistors to accelerate R&D of Ka band RF transistor on GaN/Si:

- **TRL:**  $1 \rightarrow 4$  in 3-year program

- Target performances: 30 GHz CW 3W/mm, gain>14 dB, PAE >45%. Cost/mm<sup>2</sup> to be confirmed, but <1/4 that of similar device on 4" GaN/SiC</p>

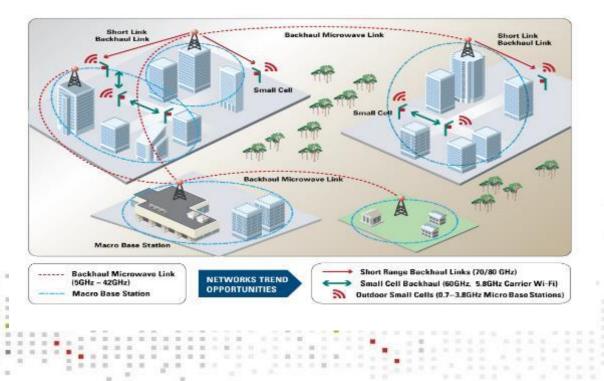

#### MOTIVATION

#### Cost reduce High performance PAs for 5G systems and ultimately, facilitate SIP integration:

200mm CMOS foundry compatible

$\rightarrow$ Larger number of PAs per wafer

$\rightarrow$ Better uniformity and higher process yield

$\rightarrow$ Better equipment uptime

→No dedicated line required (fabless/fablight business model can be implemented)

Other CMOS opportunities:

→Leverage Si implantation for ultra low resistance contacts and access regions

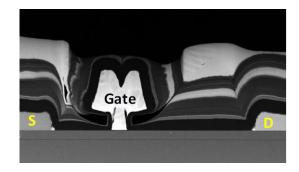

→Leverage CMOS gate know-how for mmWave PA

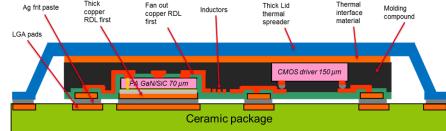

→Explore Film transfer on optimized HR substrate (ceramics...) for improved RF and/or

thermal performance (derived from LETI activity on advanced substrated with Soitec)  $\rightarrow$ Leverage 3D/TSV technology on Si (more mature than on SiC) for easier SIP integration.

CMOS compatibility constraints: Si substrate not as good thermally as SiC, more mismatched (17% vs 3,5%), No gold , No lift-off.

|3

#### LETI TEAM FOR WP2 AND MAIN STAKEHOLDERS

#### LETI Team lead engineers:

- Device Engineering: Erwan Morvan (<u>erwan.morvan@cea.fr</u>)

- « CMOS compatible »Process Engineering and WP2 key contact: Yveline Gobil (yveline.gobil@cea.fr)

- 200mm GaN/Si MOCVD : Matthew Charles (<u>matthew.charles@cea.fr</u>)

#### Main stakeholders:

- Ericsson, Thales CS & TESAT: Expecting Systems cost savings

- UMS: Expecting access to cost effective/ high volume PA Product line

- **—** Xfab as a potential 200mm foundry for GaN/Si HEMT.

- III-V Lab as R&D partner for RF design and testing of PA + comparison to GaN/SiC.

- CEA LETI Packaging Team: Post process of GaN/Si wafers for easier SIP integration

- UPadova: Assessment of GaN/Si HEMT robustness

### **KEY ACTIVITIES IN WP2 (FIRST SIX MONTHS)**

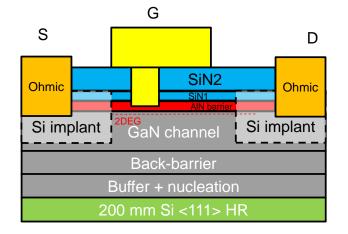

#### • Epitaxy: Optimize MOCVD epitaxy of GaN on 200mm HR Si

- Use of in-situ SiN passivation

- Optimize AIGaN and/or AIN barriers for improved Rsheet and robustness

- Optimize their effective thermal boundary resistance layer (TBReff layer)

- Reduce overall epilayers thickness and bow (20µm)

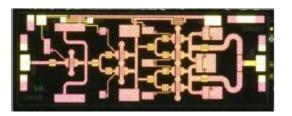

#### Validate LETI epilayer stack (GaN/Si) using III-V Lab existing GaN/SiC masks and front end process

- Epitaxial growth (MOCVD) of 200mm wafers in LETI

- Dice 3" wafers into 200mm wafers

- Process 3" wafers at III-V Lab using their masks and GaN/SiC process (gold contacts, mushroom gates by lift off)

- Test of GaN/Si HEMT at LETI (DC) and III-V Lab (HF)

#### Leti CEALERCH KEY ACTIVITIES IN WP2 (FIRST SIX MONTHS)

- Very low resistance Si implanted layers (C-MOS compatible)

- Gold-free ohmic contacts with access resistance <0,1 Ω.mm through Si implantation process optimization

• Leverage CMOS gate technology for mmW Power HEMT

• Establish a baseline process flow for 200mm CMOS compatible HEMT for Ka band (No gold, no lift off).

Prepare for SIP integration, by taking into account Packaging team requirements

Ag frit pase

Thick copper RDL

Inductors

Fan out copper RDL

Inductors

Thick Lid

Thermal

Thermal

Moding compound

Contribute to failure analysis process including electrical diagnostic and physical analysis (PFNC).

- LETI is leveraging its 200mm MOCVD epitaxy and HEMT technology platform for RF Power Amplifiers.

- LETI aims at bringing CMOS capability to the development of a cost effective GaN platform, ready for high volume manufacturing

- Benchmarking with GaN/SiC components all along

- NanoCharacterization Platform (PFNC) to contribute to characterization and failure analysis of GaN/SiC and GaN/Si devices after robustness testing.

# pionniers