High-performance computing, vital for the digital economy

High-performance computing (HPC) is a strategic challenge for the competitiveness of Europe's digital economy. To meet this challenge, the European Commission has taken the initiative of setting up EuroHPC JU, the European High-Performance Computing Joint Undertaking. It aims to bring together all the European players in this field to develop exascale supercomputers using competitive European technologies. These supercomputers should be in use by 2022.

In a highly competitive sector, exascale power, i.e. the ability of computers to perform a billion billion operations per second, is the new challenge if Europe is to remain competitive against other players such as the US, China and Japan", explains Denis Dutoit, researcher at CEA-Leti and project coordinator.

Exanode, a disruptive processor chip to reach exascale

Brought together within the European technology platform for high-performance computing, ETP4HPC, the 13 European partners in ExaNoDe drew up a research program to overcome the many difficulties of building and operating exascale systems. Within this framework, the European ExaNoDe project was launched with the main aim of resolving the challenges associated with the processor chip.

Increasing the number of cores in the processor of a chip (Moore's law) to improve its performance is no longer enough to reach exascale. The European partners in the project must base their solutions on heterogeneous computer systems, i.e. coprocessors integrating specialist functions to manage specific tasks of the supercomputer. ExaNoDe’s main aim is to provide a prototype computing software adapted to a heterogeneous system and the solution for integration into the exascale computer, based on:

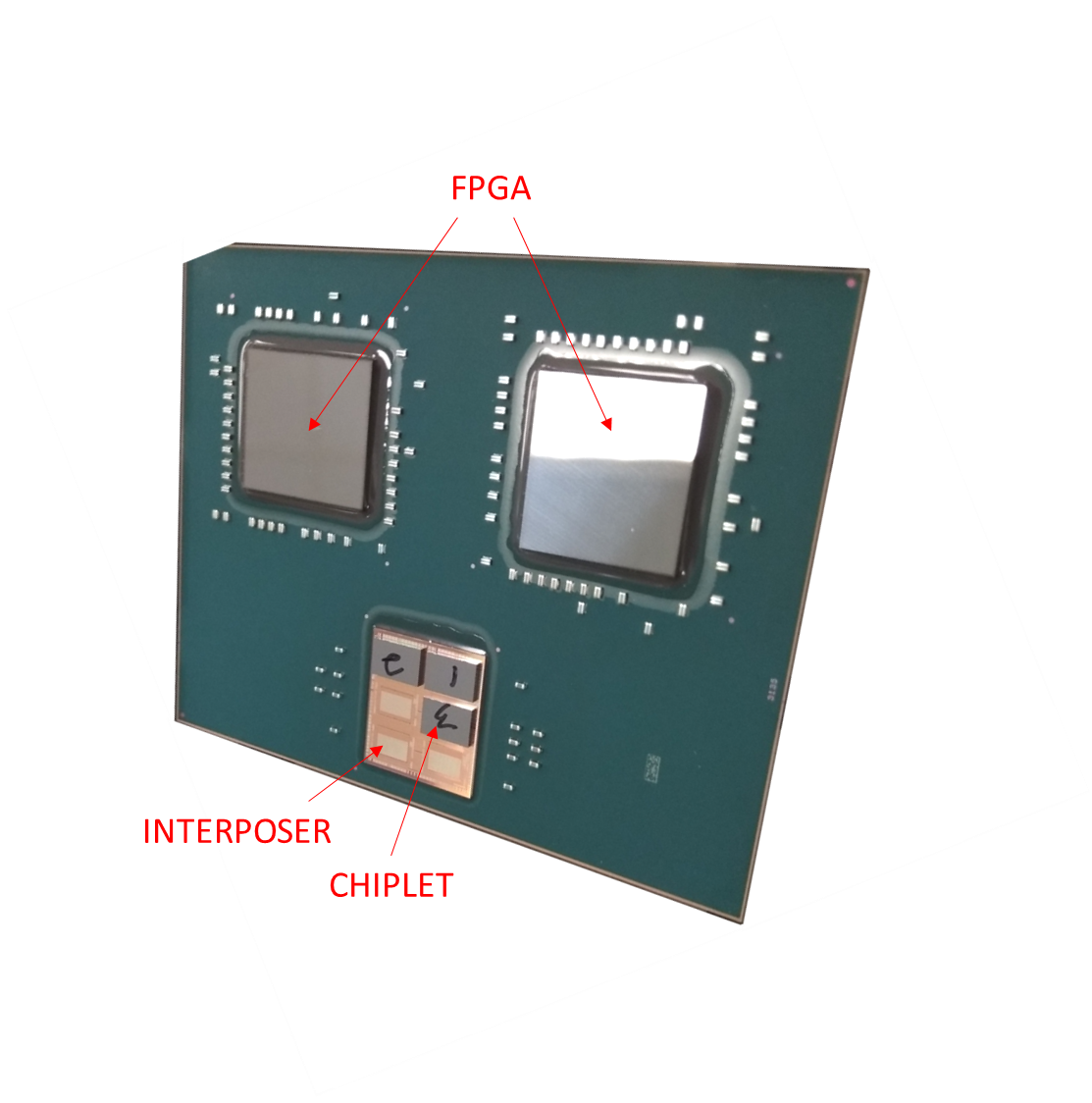

- an advanced encapsulation technology integrating a modular computing system partitioned into a number of chip stacks (MCMs) on a silicon interposer, which can interconnect the chips at low power and low cost

- a system software for testing the computing element in real applications.

Validated prototype scheduled for late June

ExaNoDe's first results cover all aspects of component integration, from the silicon technology to the system software. Concrete achievements include the design of an innovative high-speed, low-power interconnection for the heterogeneous integration of elementary chips via a silicon interposer, the 3D integration of elementary chips on an active silicon interposer with around 50,000 high-density connections, and the development of a complete software stack including system software and middleware.

In early September 2018, the ExaNoDe prototype entered its final integration phase, to demonstrate and validate all the technologies developed in the context of the project. This prototype should be validated in June. The methodology, know-how and construction blocks associated with advanced encapsulation (MCM and interposer) and the system software for heterogeneous integration provide an IP base for the next generation of processors to be used in future exascale systems. The delivery of the Exanode component consisting of a module with two FPGA chips and a 3D integrated circuit will be one of the next stages of the project.

Module with several integrated chips developed in the context of the European ExaNoDe project to increase the computing power of supercomputers @ExaNoDe