Répondre aux défis des qubits de spin des semi-conducteurs

Publié le 8 février 2024

Corps de texte 2

Pour intégrer son savoir-faire dans les technologies basées sur du silicium solide à la sphère quantique, le CEA-Leti dispose, en janvier 2021, d'une équipe aux compétences très diverses réunissant plus de 50 personnes qui travaillent sur le développement quantique, dont une grande partie de

doctorants et post-doctorants.

- Leurs expertises couvrent la micro- et nanoélectronique ; la simulation et la modélisation ; les matériaux 2D et 3D ; la conception et l'architecture de dispositifs (logique et mémoire incluses) ; le développement de masques ; l'intégration et le packaging 3D ; les circuits intégrés ; la caractérisation physique (en ligne et hors ligne) ; la caractérisation et la fiabilité électriques ; le domaine émergent de la technologie cryo-CMOS ultra basse température ; et les logiciels. Ces compétences sont complétées par le CEA-Irig et le CNRS qui réunissent des spécialistes dans le domaine de l'ingénierie quantique, de la physique des nanostructures miniaturisées et de la physique quantique.

- Le CEA-Leti, CEA-Irig, et le CNRS réunissent plus de sept équipements cryogéniques. En 2021, le CEA est le premier centre de recherche à se doter d'un nouveau prober cryogénique (de Bluefors, fabricant de référence dans le secteur de la cryogénie) pour des mesures automatiques sur des plaques 300 mm jusqu'à des températures de 2 K.

Comment le CEA-Leti prévoit-il de mettre à profit ces ressources intellectuelles et physiques pour créer des qubits sur silicium ?

- D'un point de vue stratégique, il est important de garder à l'esprit qu'en principe, le spin sur silicium représente probablement le moyen le plus simple vers la mise en œuvre d'un système quantique à deux niveaux.

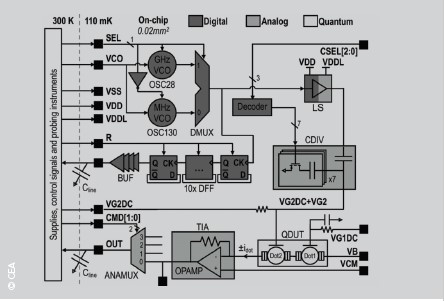

- Un exemple évident de ce potentiel est présenté dans la publication ISSCC 2020, qui décrit le circuit quantique intégré FDSOI 28 nm développé par le CEA-Leti, le CNRS et le CEA-Irig via le groupe Quantum Silicon Grenoble. Le dispositif est la première démonstration de l'intégration de qubits à des dispositifs et éléments électroniques conventionnels dotés de boîtes quantiques sur puce CMOS, associant des instruments analogiques et numériques déterminants à des structures quantiques fabriquées sur la même couche de semi-conducteur.

- La publication ISSCC indique : « le choix du silicium quantique permet à la communauté de fabricants de circuits intégrés d'intégrer des composants électroniques de contrôle des qubits à grande échelle directement [à côté] du cœur en silicium quantique, ce qui réduit considérablement le nombre de connexions et le fanout de l'adressage des qubits, et augmente en parallèle la bande passante pour la correction des erreurs et la sensibilité de lecture du spin ».

Loïck Le Guevel, co-auteur de la publication et membre du groupe de recherche Quantum Silicon Grenoble supervisé par Maud Vinet, précise que le dispositif « utilise tous les éléments nécessaires à la conception adaptée de circuits hautes performances conformes à l'état de l'art, tels que des éléments passifs, des résistances, des condensateurs et des transistors pour un fonctionnement numérique jusqu'à 7 Ghz, et des transistors pour un fonctionnement analogique jusqu'à 3 Ghz. Nous sommes qui plus est parvenus à concevoir une double boîte quantique sur la même couche de semi-conducteur que les transistors issus d'un procédé de fabrication standard. Cette réalisation souligne que la technologie FDSOI pourrait un jour permettre aux concepteurs de circuits d'utiliser des matrices de qubits embarquées au sein de blocs IP avec des composants électroniques classiques pour développer des processeurs au silicium quantique personnalisés à grande échelle ».

|

QUANTUM CIRCUIT

Functional block diagram of the mixed digital-analog

signal circuitry interfacing a quantum device at 110mk

|

Haut de page