La mémoire magnétique Spin-Orbit Torque (SOT-MRAM) est la seule technologie de mémoire non volatile assez rapide pour être utilisée au plus près de l’unité de calcul en remplacement de mémoires de type SRAM, de façon à augmenter les performances des circuits électroniques tout en diminuant fortement leur consommation énergétique. Cependant, dans le cas de SOT-MRAM, où l’aimantation est dite perpendiculaire, il a été montré que la probabilité d’écriture peut s’effondrer voire même osciller à fort courant.

Une équipe de SPINTEC, en collaboration avec la société Antaios issue du laboratoire, a quantifié ce phénomène nuisible dans des SOT-MRAM à base de couches de β W/CoFeB/MgO. En mesurant le taux d’erreur en écriture WER (Write Error Rate), elle a prouvé que ce phénomène n’était pas aléatoire mais au contraire déterministique.

Les chercheurs ont réalisé des simulations numériques dites macrospin (aimantation uniforme), basées sur des paramètres expérimentaux, qui reproduisent les cartes de WER et permettent d’expliquer le mécanisme. En injectant une impulsion de courant de forte amplitude, l’aimantation de la SOT-MRAM s’incline dans le plan, à 90° par rapport à sa direction initiale suivant l’axe -z (correspondant au bit 0). Or, cette position dynamique est instable, et à la fin de l’impulsion, durant la relaxation, les fluctuations thermiques peuvent faire revenir l’aimantation dans la direction initiale -z, faisant échouer l’écriture en laissant le bit à 0, au lieu de l’orienter dans la direction +z pour écrire le bit à 1.

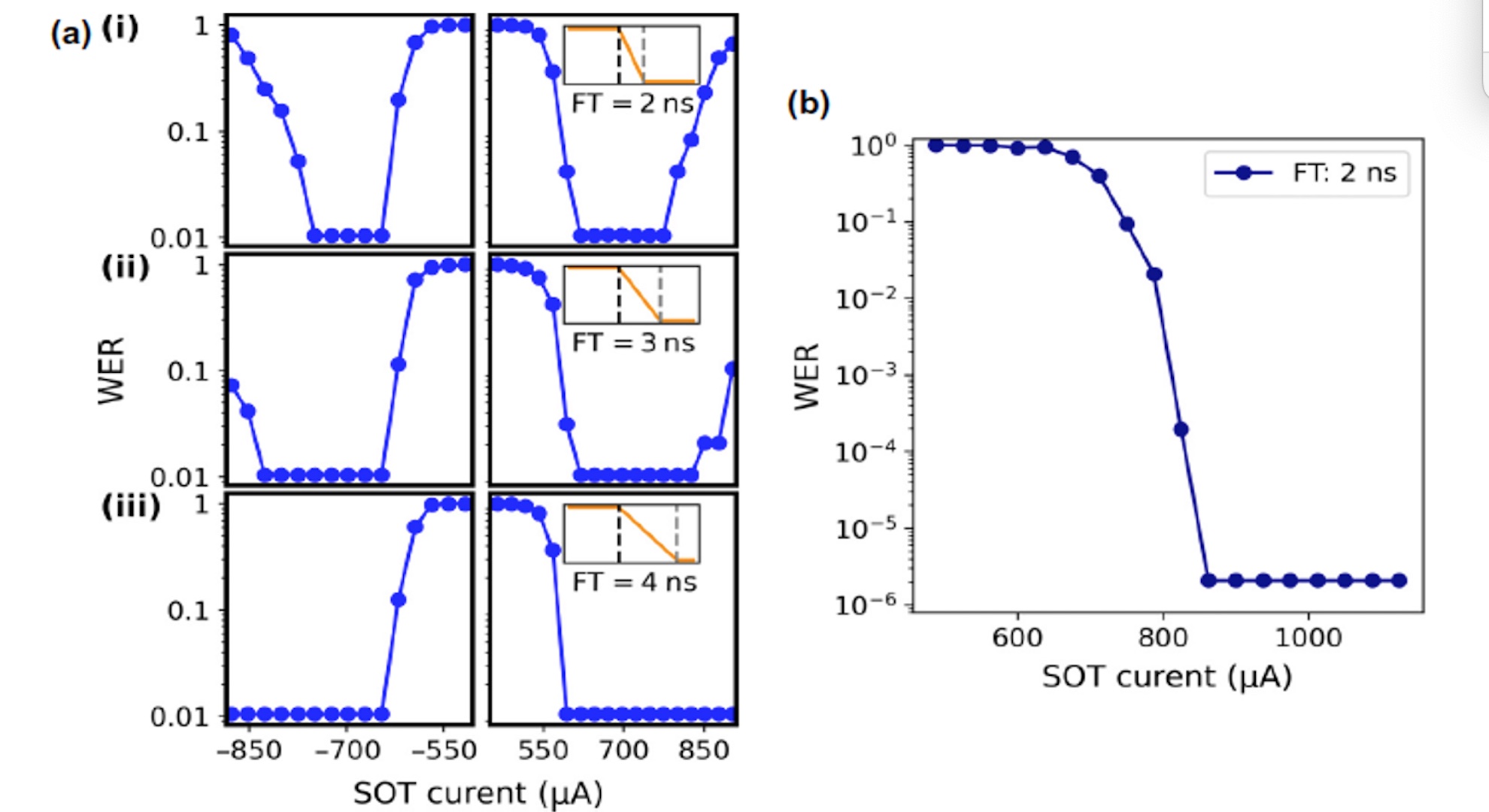

La solution simple, sans avoir besoin de recourir à des matériaux et effets physiques exotiques, est de modifier la forme de l’impulsion de courant. En prolongeant la durée de sa décroissance, le courant continue à agir sur l’aimantation au cours de la relaxation, lui permettant de s’écarter de sa position d’équilibre instable de façon contrôlée. Ainsi, pour des impulsions d’une durée de 10ns, il suffit de passer de 2ns à 4ns de descente pour éviter l’effet de back-switching.

Cette solution a été démontrée sur une cellule mémoire individuelle SOT-MRAM pour laquelle aucune erreur d’écriture n’a été détectée après des centaines de milliers de tests d’écriture cumulés (WER < 2.10−6).

Figure : (a) Augmentation de la fenêtre d’écriture d’un point mémoire simplifié (WER minimal), en fonction de la durée de décroissance de l’impulsion électrique. (b) Validation de cette solution sur une cellule mémoire complète et fonctionnelle.

Au-delà de ces résultats, ces simulations ouvrent la voie à des outils de design de circuits mémoire intégrant le back switching. Les prochains objectifs à atteindre pour le développement industriel de cette technologie sont l’obtention d’une écriture au moyen seulement d’un courant ainsi que la réduction de ce courant.

Tutelles UMR : Univ. Grenoble Alpes / CEA / CNRS / Grenoble INP

Financements : EU Horizon 2020 Marie Skłodowska Curie ITN SPEAR project (Grant 955671) ; Région Auvergne Rhône Alpes (Pack Ambition Recherche, 19 009938 01 MAPS) and the French RENATECH network implemented at the Upstream Technological Platform in Grenoble (PTA, ANR 22 PEEL 0015)

Collaborations : Société Antaios