Spin-Orbit Torque magnetic memory (SOT-MRAM) is the only non-volatile memory technology fast enough to be used in close proximity to the processing unit as a replacement for SRAM-type memories. This advancement enhances electronic circuit performance and significantly cuts down energy consumption. However, in the case of SOT-MRAM with so-called perpendicular magnetization, it has been shown that thewrite probability may collapse or even oscillate at high current.

A team from SPINTEC, in collaboration with Antaios, a company originating from the laboratory, quantified this detrimental phenomenon in SOT-MRAM devices based on β-W/CoFeB/MgO stacks. By measuring the write error rate (WER), they demonstrated that this phenomenon is not random but, on the contrary, deterministic.

The researchers performed so-called macrospin numerical simulations (assuming uniform magnetization), based on experimental parameters. These simulations reproduced the WER maps and elucidated the underlying mechanism. When a high-amplitude current pulse is injected, the magnetization of the SOT-MRAM tilts into the plane, at 90° from its initial direction along the -z axis (corresponding to bit 0). However, this dynamic position is unstable, and at the end of the pulse, during the relaxation phase, thermal fluctuations may drive the magnetization back to its initial -z direction, causing the write operation to fail by leaving the bit in state 0, instead of orienting it toward the +z direction to write bit 1.

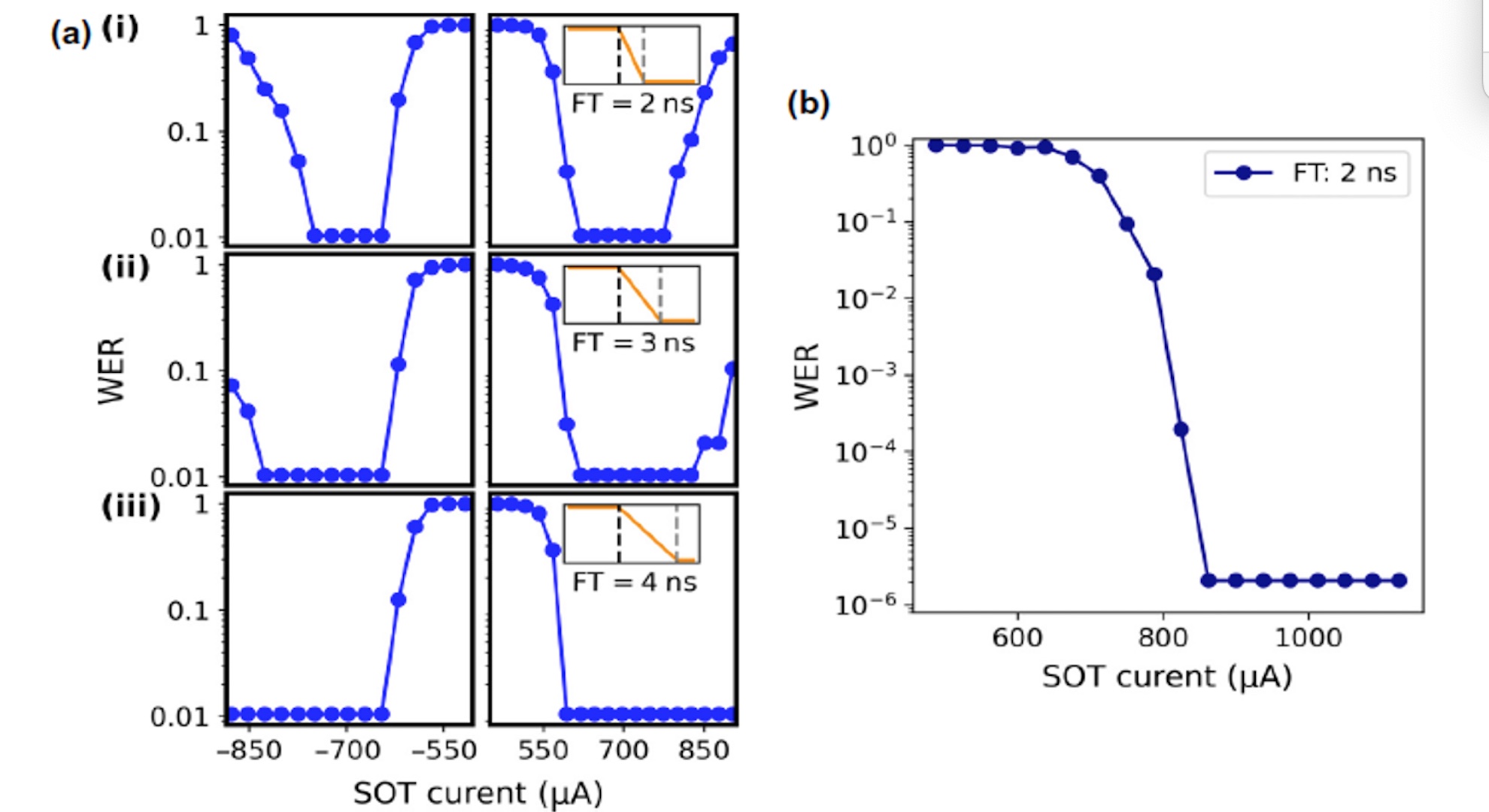

A straightforward solution, without relying on exotic materials or physical effects, involves modifying the shape of the current pulse. By extending the decay time of the pulse, the current continues to act on the magnetization during relaxation, allowing it to move away from its unstable equilibrium position in a controlled manner. Thus, for pulses with a duration of 10 ns, increasing the fall time from 2 ns to 4 ns is sufficient to prevent the back-switching effect.

This solution was successfully demonstrated on an individual SOT-MRAM memory cell, for which no write errors were detected after several hundred thousand cumulative write tests (WER < 2 × 10⁻⁶).

Figure: (a) Increase in the write window of a simplified memory element (minimum WER) as a function of the electrical pulse fall time. (b) Validation of this solution on a complete and functional memory cell.

Beyond these results, these simulations pave the way for memory-circuit design tools that incorporate back-switching. The next objectives for the industrial development of this technology are to achieve writing using current alone and to reduce the amplitude of that current.

Spintec is a Common Research Unit (UMR): Univ. Grenoble Alpes / CEA / CNRS / Grenoble INP

Fundings: EU Horizon 2020 Marie Skłodowska Curie ITN SPEAR project (Grant 955671) ; Région Auvergne Rhône Alpes (Pack Ambition Recherche, 19 009938 01 MAPS) and the French RENATECH network implemented at the Upstream Technological Platform in Grenoble (PTA, ANR 22 PEEL 0015)

Collaboration: Société Antaios