Quel est le contexte en 1995 ?

Simon Deleonibus : La microélectronique visait à « faire » toujours plus petit et plus rapide, et moins gourmand d'énergie mais on sentait arriver les limites de la miniaturisation des transistors MOSFET (Metal Oxide Semiconductor Field Effect Transistor). Au bout de cette logique, la communauté de la microélectronique se heurtait à des effets « limites ». Par exemple : l'effet tunnel direct à travers l'isolant de « grille » (oxyde de silicium, le O de MOSFET) qui sépare l'électrode de commande du transistor (grille) du « canal » (par lequel transitent les électrons). Les électrons traversent alors l'isolant devenu trop mince. Pour réduire ces fuites de courant indésirables, nous avons remplacé l'oxyde de silicium par de l'oxyde d'hafnium.

Simon Deleonibus : La microélectronique visait à « faire » toujours plus petit et plus rapide, et moins gourmand d'énergie mais on sentait arriver les limites de la miniaturisation des transistors MOSFET (Metal Oxide Semiconductor Field Effect Transistor). Au bout de cette logique, la communauté de la microélectronique se heurtait à des effets « limites ». Par exemple : l'effet tunnel direct à travers l'isolant de « grille » (oxyde de silicium, le O de MOSFET) qui sépare l'électrode de commande du transistor (grille) du « canal » (par lequel transitent les électrons). Les électrons traversent alors l'isolant devenu trop mince. Pour réduire ces fuites de courant indésirables, nous avons remplacé l'oxyde de silicium par de l'oxyde d'hafnium.

Mais plus fondamentalement, la petitesse du canal était, elle aussi, à l'origine de fuites qui pouvaient devenir incontrôlables. On voyait apparaître des effets au 2e ordre qui risquaient de passer au 1er ordre. Perdre un électron sur quelques dizaines à l'échelle de 20 nm n'a pas le même impact qu'en perdre un sur quelques milliers à l'échelle de 100 nm ! Ces effets remettaient en cause non seulement le fonctionnement des composants numériques et analogiques mais aussi celui des circuits mémoires, en particulier les mémoires non volatiles auxquelles le CEA-Leti consacrait un programme important.

Il fallait préparer la microélectronique du futur et mettre en place des collaborations tant avec la Direction de la recherche fondamentale du CEA (DRF) que d'autres laboratoires académiques nationaux et internationaux.

Avec Jacques Gautier du Leti, nous avons fait un tour du monde en 1995 : Universités de Stanford, Berkeley, Harvard, Columbia, SUNY, MIT, Toshiba, Hitachi, Fujitsu, Université de Tokyo, Riken, etc. De cet état des lieux, il est ressorti que tous les labos travaillaient sur deux thématiques majeures : les limites de la technologie CMOS et de sa miniaturisation d'une part et la recherche d'alternatives, tant du point de vue des composants que des nouveaux paradigmes du calcul informatique, d'autre part. De nombreux labos universitaires travaillaient sur les semi-conducteurs III-V (GaAs, GaAlAs, InGaN, etc.) car ils offraient la possibilité de mettre en évidence des effets quantiques limites sans aller vers une miniaturisation extrême. Se procurer une lithographie et du silicium à l'état de l'art n'était pas à la portée de toutes les bourses des labos académiques…

Votre collaboration démarre en 1996 avec PLATO… De quoi s'agit-il ?

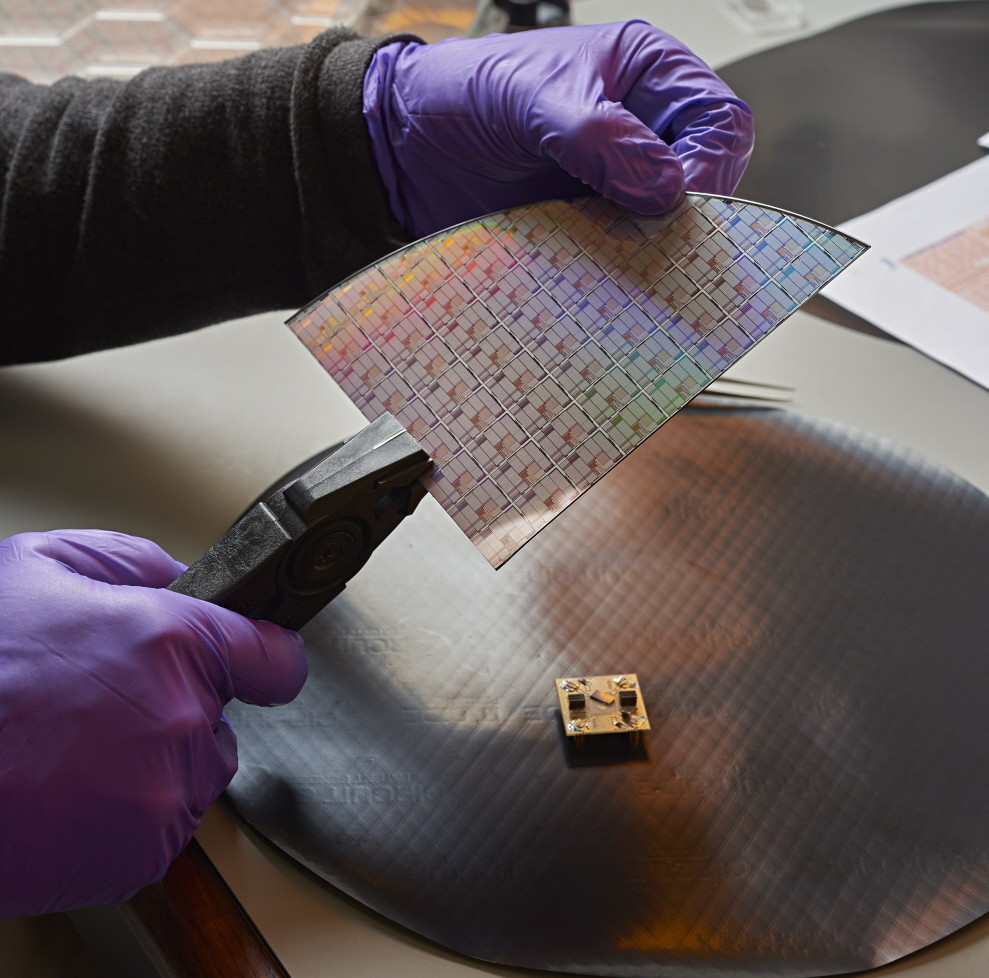

SD : Avec les encouragements de Jean Therme, alors responsable de la microélectronique au Leti, nous avons créé le programme « PLATO Microélectronique du futur » en 1996. L'objectif est à la fois de repousser les limites de l'existant – le transistor à effet de champ MOSFET– et de susciter des ruptures technologiques. En référence au philosophe Platon, symbole de connaissance, on avait choisi de l'appeler PLATO, que nous avons ensuite décliné en « plateforme technologique ouverte ». PLATO, c'était donc à la fois un accès privilégié à des moyens de fabrication au meilleur niveau pour les chercheurs académiques et, pour nous, une porte ouverte sur la communauté scientifique française et internationale. En un an, nous avons monté près de cent projets, avec Marc Sanquer et de nombreux autres partenaires (Insa Lyon, Institut Néel, IEF, etc) et avons fourni des tranches de silicium comptant de très nombreux composants à tester !

Marc Sanquer : Le binômage avec Simon Deleonibus a commencé avec l'ouverture d'une salle blanche du Leti à la recherche fondamentale (PLATO). Notre idée était d'explorer le comportement de transistors à très basse température. Avec une curiosité de chercheur fondamentaliste, on s'est mis à mesurer les caractéristiques de transistors standard : à 4 K, 1 K, 50 mK. On s'est rendu compte que le transport de courant fonctionnait de manière très différente à ces températures et à température ambiante. Ainsi par exemple, quand la tension de grille de contrôle du transistor croît aux bornes du transistor, le courant oscille au lieu d'augmenter ! On s'attendait à des ruptures fondamentales. Nombre d'entre elles avaient été mises en évidence dans les semi-conducteurs III-V mais le silicium présentait un cas différent : un oxyde très performant, une capacité de fabrication via PLATO de dispositifs au moins dix fois moins longs, une « structure de bande » électronique complexe mais permettant de jouer sur différentes « vallées » et sur le « couplage spin-orbite », et, enfin nous y reviendrons, la quasi-absence de spins nucléaires après purification isotopique. Tous ces aspects ont joué un rôle par la suite.

Marc Sanquer : Le binômage avec Simon Deleonibus a commencé avec l'ouverture d'une salle blanche du Leti à la recherche fondamentale (PLATO). Notre idée était d'explorer le comportement de transistors à très basse température. Avec une curiosité de chercheur fondamentaliste, on s'est mis à mesurer les caractéristiques de transistors standard : à 4 K, 1 K, 50 mK. On s'est rendu compte que le transport de courant fonctionnait de manière très différente à ces températures et à température ambiante. Ainsi par exemple, quand la tension de grille de contrôle du transistor croît aux bornes du transistor, le courant oscille au lieu d'augmenter ! On s'attendait à des ruptures fondamentales. Nombre d'entre elles avaient été mises en évidence dans les semi-conducteurs III-V mais le silicium présentait un cas différent : un oxyde très performant, une capacité de fabrication via PLATO de dispositifs au moins dix fois moins longs, une « structure de bande » électronique complexe mais permettant de jouer sur différentes « vallées » et sur le « couplage spin-orbite », et, enfin nous y reviendrons, la quasi-absence de spins nucléaires après purification isotopique. Tous ces aspects ont joué un rôle par la suite.

SD : On a fait de la « leçon de choses » en quelque sorte, on a appris de l'existant, on a vérifié que nos idées étaient les bonnes. C'était un peu l'aventure… Je me souviens de la réflexion de Marc après avoir analysé nos premiers échantillons. « Je peux tester vos composants plusieurs fois, ils sont toujours vivants ! » Les autres composants étaient loin de bénéficier de la même maturité technologique.

Avec Marc Sanquer et son équipe, nous définissions et exploitions ensemble les manips – nous avons pu ouvrir nos cahiers de labo – et nous mettre d'accord sur leur interprétation. Nous étions copropriétaires des idées. On peut dire que cette cogestion de projets a été une réussite : elle a été transmise ! Nous en sommes aujourd'hui à la 6e ou 7e génération de chercheurs « héritiers ».

En 1999, 2000, 2003, arrivent les grandes premières. Comment sont-elles accueillies ?

SD : En 1999 , nous avons réalisé le plus petit transistor du monde de l'époque ! Les circuits les plus avancés dans l'industrie étaient basés sur une technologie de transistors MOS de longueur 180 nm. Nous avons raccourci cette géométrie à 20 nm. Les ministères chargés de la recherche et de l'industrie et le CEA ont annoncé notre résultat publié dans la revue scientifique IEEE Electron Device Letters. Toute la presse quotidienne, les radios, les télévisions nationales et internationales se sont fait l'écho de l'évènement.

Nous avions exploré le comportement de canaux de dimensions nanométriques afin d'orienter la technologie qui serait utilisée dans nos téléphones portables, quinze ans plus tard. Cette anticipation était nécessaire, compte tenu de l'ampleur de la tâche qui nous attendait : le développement des architectures du type Fully Depleted Silicon On Insulator (FDSOI) et plus encore celui des transistors à grille « enrobante » (avec des canaux à nanorubans ou nanofils). Le CEA-Leti avait de nombreux atouts dans ce domaine grâce à sa maîtrise unique de la fabrication de substrats SOI.

Après ce record, on nous a regardés avec plus de bienveillance. Ça nous a permis de nous ouvrir davantage à la communauté scientifique internationale. Ça a fait boule de neige. Nous avons pu augmenter le recrutement de scientifiques de bon niveau. Parmi eux, certains venaient de la DRF ou des laboratoires académiques avec lesquels nous collaborions.

A 20-nm physical gate length NMOSFET featuring 1.2 nm gate oxide, shallow implanted source and drain and BF2 pockets, IEEE Electron Device Letters (2000)

MS : De nombreux scientifiques travaillaient sur un effet « mono-électronique » appelé blocage de Coulomb. De quoi s'agit-il ? Quand un électron se présente dans le canal d'un transistor, il ne peut passer que si le canal est énergétiquement « indifférent » à l'ajout d'un électron. Si ce n'est pas le cas, il y a « blocage de Coulomb », l'électron ne passe pas et le courant entre électrodes du transistor (drain – source) s'éteint, ce qui explique les oscillations déjà mentionnées. En 1998, nous avons mis en évidence, pour la première fois, cet effet surprenant dans un transistor MOSFET qui n'était pourtant pas optimal pour ces expériences.

Coulomb oscillations in 100 nm and 50 nm CMOS devices, IEEE (1999)

SD : Nous avions besoin de comprendre plus en profondeur le blocage de Coulomb. Était-il seulement gênant ou pouvait-il être utile ?

Avant de pouvoir faire du blocage de Coulomb dans des transistors à nanofils reproductibles et fiables, nous avons utilisé des « boîtes quantiques » de quelques nm de diamètre pour ces manips. Pour les fabriquer, nous avions adapté nos technologies de dépôt de silicium polycristallin pour produire des nanocristaux individuels de silicium. Enrobé d'un isolant, cet objet pouvait piéger ou perdre des électrons en très faible quantité, voire un par un. Une charge unitaire piégée dans un nanocristal a permis de manipuler le blocage de Coulomb dans un canal de MOSFET. Mené en parallèle, le développement technologique des nanocristaux de silicium a eu des retombées pour l'intégration de mémoires non volatiles, commercialisées plus tard par STMicroelectronics et Freescale.

Single electron charging and discharging phenomena at room temperature in a silicon nanocrystal memory, Solid-State Electronics (2003)

Manipulation of periodic Coulomb blockade oscillations in ultra-scaled memories by single electron charging of silicon nanocrystal floating gates, IEEE Transactions on Nanotechnology(2005)

MS : En utilisant le blocage de Coulomb, nous avons appris à contrôler les électrons un par un dans le canal d'un transistor CMOS, en 2003. On était les premiers et les seuls à le montrer dans un transistor CMOS. Quelques industriels japonais seulement (NTT en particulier), avaient conservé une activité de recherche sur le silicium.

Controlled single-electron effects in non-overlapped ultra-short silicon field effect transistor, IEEE transactions on Nanotechnology (2003)

Et puis, vient le temps des projets européens. Quel regard portez-vous sur cette période ?

MS : Au début de la collaboration, nos échantillons n'étaient pas prioritaires. On était un peu des extraterrestres et on sentait à notre égard une curiosité amusée. Et puis la série de contrats européens – pour la plupart, coordonnés par nous – a permis d'asseoir progressivement nos activités à Grenoble. Les collègues du Leti ont vu qu'on avait du répondant. Et aujourd'hui, je suis très content que cette thématique soit devenue un « vrai » programme européen du Leti !

SD : Aujourd'hui, l'introduction de nouveaux composants ou de technologies de rupture va de pair avec des recherches collaboratives fortes, la motivation des chercheurs est primordiale. Dans le domaine de la high tech, il faut y ajouter des moyens technologiques lourds, comme ceux du CEA. Suite au succès de notre collaboration, le CEA nous a soutenus par des programmes internes (couplage Direction des sciences de la matière – Direction de la recherche technologique, etc.) complétant des financements de collaborations à l'extérieur du CEA. Par exemple, AFSID, le premier projet collaboratif européen que nous avons coordonné (voir ci-dessous) a ouvert des applications originales et variées, dérivées du blocage de Coulomb : mémoires non volatiles ou encore pompes à électrons pour la métrologie, génération de nombres aléatoires ou signatures indélébiles de transistors individuels.

MS : AFSID a été considéré comme un succès par la Commission européenne. Ce projet nous a aussi rapprochés de l'Université de Melbourne, spécialiste de l'implantation de dopant unique. Avec un dopant unique de phosphore dans le canal, on a pu étudier un transistor à atome unique puis à deux atomes uniques, dans lesquels les électrons passent par les orbitales atomiques d'un ou deux dopants de phosphore.

Single donor ionization energies in a nanoscale CMOS channel, Nature Nanotechnology (2010)

Detection of a large valley-orbit splitting in silicon with two-donor spectroscopy, Phys. Rev. Lett. (2012)

Une thématique nouvelle s'ouvrait car ces expériences, développées parallèlement par des australiens, constituaient des premières.

Il y a eu également TOLOP (voir ci-dessous), avec des applications très basse énergie, SIAM (idem) sur les pompes à électrons et SISPIN (idem), consacré au spin des électrons, qui annonce la montée en puissance des recherches européennes sur le quantique (ERC Synergy QuCube et Flagship On Quantum Energy) et pour lequel nous avons reçu le Trophée des Étoiles de l'Europe en 2017.

Le quantique entre en scène en 2016 avec l'annonce du premier bit quantique CMOS, puis l'ERC Synergy et le Flagship On Quantum Computing (voir ci-dessous). Comment la bascule s'opère-t-elle ?

MS : Alors que les basses températures limitaient jusque-là les applications à des niches, le quantique a cassé la contrainte sur la température. Un bit quantique ne peut fonctionner qu'à basse température. Ça a libéré les idées ! Le « comptage » d'électrons permettait-il de fabriquer un bit quantique ? En réalité, non, la charge électrique de l'électron conduit à un dispositif qui n'est pas assez stable. Notre choix s'est donc porté sur le spin de l'électron, une propriété purement quantique : l'électron est fixe et seul son spin est modifié quand le bit associé change de valeur.

SD : En parallèle, le transistor évolue vers une structure à nanofil, déjà évoquée. La miniaturisation rendant toujours plus difficile le contrôle des fuites, il faut « sécuriser » davantage le chemin des électrons et donc, entourer complètement le canal d'isolant. Le canal doit lui-même être recouvert par l'électrode qui contrôle le passage des électrons (grille). Ces impératifs conduisent à la forme cylindrique du canal, contenu dans un nanofil de silicium. La grille et l'isolant de grille, déposés sur le nanofil, enrobent le canal partiellement, voire totalement.

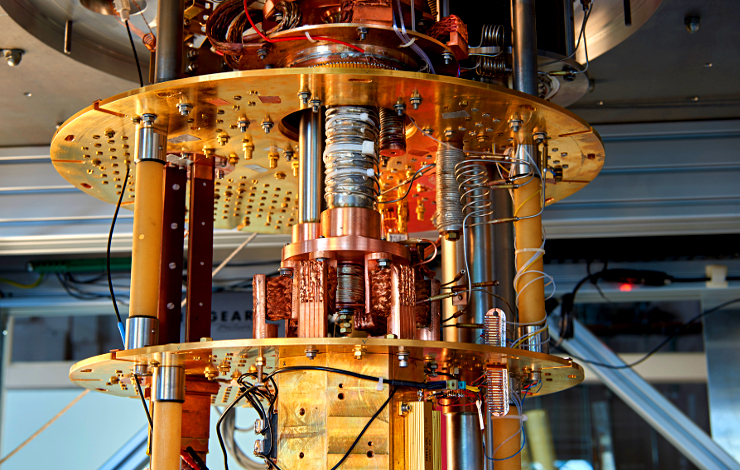

MS : En 2016, nous réalisons le premier bit quantique CMOS avec un transistor FD-SOI dont le canal est un nanofil de silicium de section 10×20 nm², recouvert de deux grilles de 30 nm de longueur en série. Sous chaque grille, un électron est d'abord piégé. Le spin du 1er électron peut être manipulé grâce au champ électrique créé par cette 1re grille – c'était une vraie prouesse – tandis que le spin du 2e électron est figé. Ici, c'est l'état de spin du 1er électron qui permet d'encoder l'information quantique. Pour lire cette information, on utilise le principe de Pauli qui interdit le transfert de charge lorsque les spins des deux électrons sont identiques.

En réalité, nous n'avons pas fait l'expérience avec des électrons mais avec des trous, c'est-à-dire des lacunes d'électrons, car le spin des trous est sensible au champ électrique – facile à manipuler dans un transistor à effet de champ – et celui des électrons au champ magnétique. L'inconvénient des trous est qu'ils sont plus lourds que les électrons et « voient » davantage les défauts du transistor. Une voie de recherche actuelle vise à étudier comment utiliser plutôt les électrons.

Un autre point concerne le matériau silicium. L'isotope majoritaire du silicium (28Si) ne porte pas de spin nucléaire, à la différence des atomes Ga et As dans les boîtes quantiques et de l'isotope minoritaire du silicium (29Si), présent à hauteur d'environ 5 % dans le silicium naturel. Pour que les trous « voient » autour d'eux un « vide » de spin, il faut utiliser du silicium 28 le plus pur possible, avec moins de 0,006 % de 29Si. Nous avons réalisé cette purification et espérons voir une augmentation drastique de la cohérence de nos trous.

Personne ne sait quel bit quantique sera utilisé dans les futurs processeurs quantiques. Aujourd'hui, le qubit CMOS n'est ni le premier ni le meilleur, mais il ouvre la microélectronique CMOS au monde quantique et à ses promesses de rupture.

A CMOS silicon spin qubit, Nature Communications (2016)

SD : Je partage ce point de vue. Aujourd'hui, la micro ou nanoélectronique sur silicium traite une quantité d'informations que nous n'aurions pas imaginée il y a 50 ans et nous sommes arrivés à la croisée des chemins prédite, dès le milieu des années 2000, par la « feuille de route » des semi-conducteurs (International Technology Roadmap of Semiconductors) à laquelle j'ai contribué. La réduction de la taille des composants (suivant 2 dimensions) pourrait désormais ralentir, voire s'arrêter, au-delà de 2030.

Dès 2004, des alternatives à l'augmentation du nombre de composants par puce (selon la loi dite de Moore) ont été identifiées. L'ordinateur quantique apparaissait intéressant pour le calcul massivement parallèle, les architectures « neuromorphiques » et programmables pour la résilience des systèmes, des interfaces, des capteurs intelligents, la gestion de la consommation, etc. Chaque option a été comparée à ses concurrentes, comme l'avaient été les technologies à base de semi-conducteurs dès 1997, avec une vision à 15 ans. Le calcul quantique devra être soumis à la même démarche critique.

Un registre de n bits quantiques contient à tout instant 2n informations au lieu de n, en informatique classique. Cette propriété désigne le traitement massivement parallèle de données (sur internet ou dans des bases de données à forte capacité) et les problèmes de factorisation comme les applications phares du calcul quantique.

La mise en œuvre de ces bits quantiques se heurte cependant à des défis de taille, tant au niveau de la technologie, qu'à celui de l'architecture des circuits et des ordinateurs. Il faudra en particulier augmenter la part de déterminisme dans les procédés de fabrication, tout en diminuant les éléments parasites pouvant perturber l'état d'une particule ou d'un atome unique. Et il sera primordial de réussir à exploiter la 3e dimension pour raccourcir les distances entre blocs de circuits et minimiser les perturbations de signaux et les temps de latence.

Les équipes du CEA et leurs partenaires académiques nationaux (CNRS, universités, etc.), internationaux et industriels sont bien armés pour relever ces défis et tracer le chemin vers de futures applications !

Relire aussi quelques actualités de la DRF :