C’est lancé ! Le CEA a ouvert à ses partenaires industriels et académiques la ligne pilote FAMES, dédiée à la maturation de cinq technologies-clefs de la microélectronique, afin de favoriser l'émergence de puces plus performantes, plus sobres en énergie et moins gourmandes en ressources planétaires. C’est le résultat d’un investissement de près d’un milliard d’euros, co-financé dans le cadre du Chips Act par la Commission européenne et les Etats membres dont l’État français à travers France 2030. Objectif : mettre au point et transférer aux industriels les technologies qui contribueront aux produits de demain.

Nouvelle salle blanche de la ligne pilote Fames © Equans

« Les puces interviennent presque partout, rappelle Thomas Ernst, directeur scientifique au CEA. Ce n’est pas qu’une question d’ordinateur ou de smartphone ! » Même chez les industriels dont ce n’est pas le cœur de métier, les composants s’imposent, dans les moyens de production ou le produit final. Principal moteur du secteur : la miniaturisation, qui engendre une baisse des coûts, et générant une démocratisation des puces électroniques. Côté calcul, pour les transistors, les nœuds les plus avancés chez les fabricants asiatiques atteignent 2 nm.

Les différentes architectures

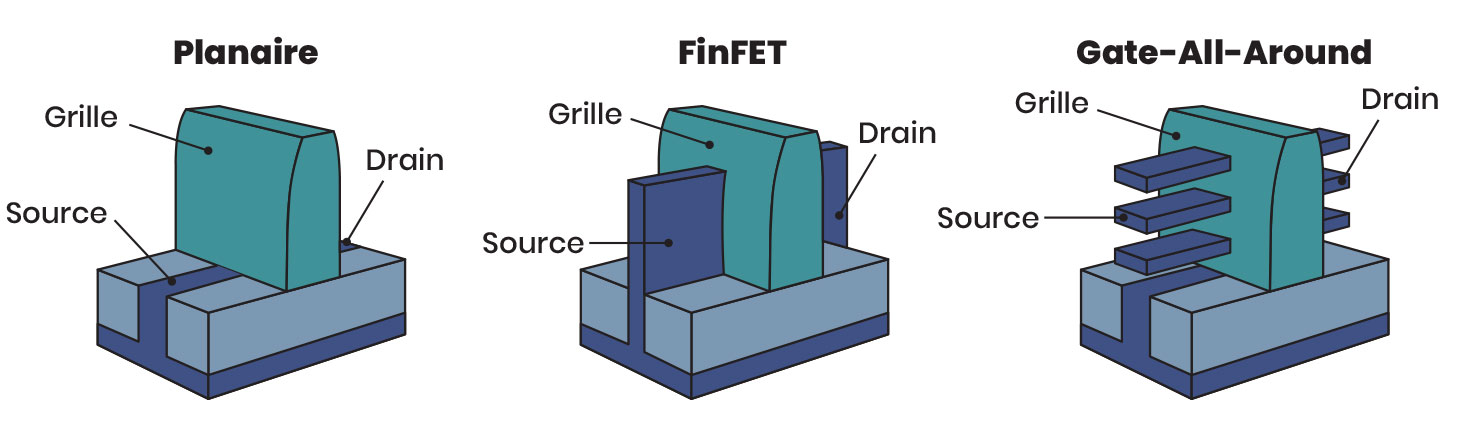

La miniaturisation s’accompagne d’un changement d’architecture. Jusque-là, la plus répandue est le MosFET planaire, un type de transistor où le film actif est horizontal. Pour des composants plus petits, en-dessous du nœud 17nm, on trouve le FinFET. Sa structure verticale, en aileron, permet de réduire les fuites de courant et d’améliorer le contrôle.

Pour l’avenir, l’industrie du semi-conducteur mise sur le GAA et son architecture de grille « enrobante » sur laquelle le CEA travaille depuis les années 2000. Ce sont alors des nanofils ou des nanofeuilles de silicium qui s’empilent et sont enrobés par la grille. Avec, là encore, moins de fuites de courant et donc une meilleure performance énergétique. Ces transistors de dernière génération sont déjà en cours de production chez Samsung et TSMC. Et la créativité des concepteurs ne s’arrête pas là, avec tout un annuaire de nouveaux transistors FET.

Les différentes architectures de transistors © CEA/Bear Ideas

Toutefois, plus on tend vers l’infiniment petit, plus des effets quantiques indésirables apparaissent. Sans entrer dans les détails, les électrons « sautent » au lieu de transiter correctement. Résultat, le rythme de miniaturisation des transistors ralentit ces dernières années.

Chiplets et intégration 3D

Côté mémoire et interconnexions, on touche également aux limites. Or, la quantité de données augmente sans cesse.

« Imaginez passer d’un village de 300 habitants à une ville de 3 millions et vous cherchez quelqu’un, compare Thomas Ernst. Pour réussir dans un temps acceptable, vous devez découper votre mégalopole en petites zones et envoyer des détectives partout. »

Pour cela, le CEA possède un savoir-faire reconnu, combinant la miniaturisation, avec de nouvelles technologies de mémoires moins consommatrices, et l’intégration 3D. « L’approche 3D sur laquelle nous travaillons depuis plus de 20 ans permet un gain de place et des interconnexions plus nombreuses et donc une meilleure performance », résume Thomas Ernst.

« Il s’agit, à gros traits, de découper les différents composants de la puce (calculs, mémoires, entrées/sorties) pour les fabriquer avec des nœuds technologiques différents, puis soit de les empiler, soit de les mettre côte à côte », simplifie Alexandre Valentian, à la tête du Laboratoire systèmes sur puce et technologies avancées au CEA. Cette technique repose sur des chiplets, des circuits à la fonctionnalité unique qui sont assemblés comme une seule puce. Cette évolution de l’architecture des puces électroniques à base de chiplets ressemble en quelque sorte à un Lego, avec des briques assemblées, là où les puces classiques seraient plutôt des Playmobil, fabriquées d’un seul tenant.

Ces architectures de puce à base de chiplets et d’intégration 3D apportent des avantages significatifs : une amélioration des performances et une réduction des coûts de fabrication, grâce à l’utilisation de la technologie la plus adaptée, et non forcément la plus avancée.

« Fabriquer des transistors avancés coûte très cher, car il faut une très haute précision de gravure », débute Alexandre Valentian. Les machines de lithogravure à cette échelle sont dites « extrême UV ». Le dernier modèle produit par ASML, leader mondial du marché, coûte à lui seul plus de 400 millions d’euros. Comptez 6 mois et 250 personnes pour assembler l’engin, de la taille d’un bus. « Avec une approche chiplet, vous pouvez ne fabriquer que la partie calcul dans ce nœud avancé et garder des lignes de production moins coûteuses pour les autres composants », explique-t-il.

La spintronique

Mélange d’électronique et de quantique, la spintronique, qui utilise le spin des électrons en plus de leur charge électrique, contribue également aux puces du futur… mais aussi des puces d’aujourd’hui !

« Ces dispositifs permettent de réaliser les mêmes opérations que celles obtenues avec de la microélectronique, mais plus rapidement ou en demandant moins d’énergie, résume Lucian Prejbeanu, à la tête du laboratoire Spintec. C’est une brique de base, qui peut s’appliquer à plusieurs technologies, comme les mémoires et les capteurs magnétiques, ou les composants radiofréquences. L’industrie automobile utilise déjà des capteurs spintroniques pour l’enregistrement de position ou de vitesse. »

Tests de composants au laboratoire Spintec © D. Guillaudin/CEA

Au niveau européen, le réseau Spintronic Factory, auquel participe le CEA, explore les possibilités d’applications industrielles. La spintronique apporte aussi des solutions frugales pour les architectures de calcul optimisées, dont certaines bio-inspirées. Ces travaux font l’objet du PEPR Spin, copiloté par le CEA et le CNRS et soutenu par France 2030. Côté mémoires, « les concepts spintroniques permettent d’éviter une consommation d’énergie en veille, et de réaliser directement le calcul dans la mémoire, au plus proche du stockage, évitant ainsi la dépense énergétique de la transmission des données entre mémoire et processeur », détaille Lucian Prejbeanu, qui copilote le PEPR.

L'avenir du FD-SOI

Fidèle à son histoire, le CEA continue d’améliorer le FD-SOI, technologie phare développée à Grenoble et adoptée par de grands noms comme STMicroelectronics, Qualcomm, Sony, Google, NXP, Nordic ou Samsung. Dans le cadre du projet de ligne pilote FAMES instruit dans le cadre du Chips Act Européen, une réduction de taille est en cours, avec des nœuds de 10, puis 7 nm. Si cela reste des nœuds plus grands que ceux en production en Asie, c’est qu’ils ne répondent pas aux mêmes besoins de circuits.

Démonstrateur d'un transistor FD-SOI 7-10 nm © S. Barbier/CEA

Là où les fonderies* asiatiques produisent surtout des composants pour le calcul, le FD-SOI se concentre sur des fonctionnalités précises, par exemple pour les capteurs automobiles ou les objets connectés. « La recherche de performance tend à réaliser des circuits toujours plus spécialisés et optimisés au lieu d’une approche généraliste », confirme Alexandre Valentian. Comparé au FD-SOI 28 nm, ce modèle réduit devrait apporter un gain de consommation énergétique d’un facteur trois à quatre selon les applications. Car qu’elle soit petite ou grande, à transistor planaire ou enrobée, en version chiplets ou non, la puce du futur se devra d’avoir une moindre empreinte environnementale. Et ce, de sa conception jusqu’à sa fin de vie.

* Une fonderie est un fabriquant de composants semi-conducteurs, comme TSMC, STMicroelectronics ou encore GlobalFoundries.

Des substrats innovants

Dans la lignée de la technique Smart CutTM, inventée par Michel Bruel au CEA en 1991 et utilisée pour intégrer la couche d’isolant dans le FD-SOI, et avec des partenaires comme Soitec – avec lequel il a créé le Substrate Innovation Center – le CEA travaille sur de nouvelles générations de substrats, les plaques sur lesquelles on réalise les composants. « Il s’agit de mettre les matériaux uniquement là où ils sont nécessaires, sans gaspillage, et de fabriquer des composants auxquels on apporte le moins d’énergie possible en entrée », explique Thomas Ernst.

Les chercheurs s’intéressent aux alternatives au silicium pour des applications où ce dernier n’offre pas les meilleures performances, par exemple le carbure de silicium (SiC) pour la conversion d’énergie dans les véhicules électriques. Mais ce matériau n’est pas bon marché au niveau de la qualité cristalline requise. « D’où l’idée d’adapter la technologie Smart CutTM pour transférer une très fine couche d’un substrat SiC sur un substrat silicium, lequel sert de support mécanique et est moins cher, décrit Carlos Beitia, responsable de la ligne de programmes Matériaux. C’est la technologie SmartSiCTM, développée avec Soitec en 2020. »

Même problématique pour la photonique intégrée sur silicium. Derrière cette appellation, il s’agit d’amener la lumière à l’intérieur des circuits : sur de grandes distances, les informations sont échangées par fibre optique, mais entre composants, elles transitent électroniquement.

Une puce photonique réalisée par le CEA en cours d'analyse. © L. Godart/CEA

Réussir à « miniaturiser la fibre optique » permettrait de passer par les photons et non les électrons, avec un gain du débit d’information pour une même consommation énergétique. Pour cela, les matériaux explorés, tel le nitrure de gallium (GaN), ont besoin de substrats différents qu’il faut développer et tester.

Réemploi et recyclage des composants

En aval, le CEA participe au projet européen EECONE, qui vise à développer dès le départ des composants facilement réparables et recyclables en fin de vie. Côté réemploi, l’un des freins à la revente de téléphones et d'ordinateurs réside dans la présence de données sensibles. Avec des partenaires académiques et des entreprises spécialisées et le soutien de l’ADEME, le CEA explore l’utilisation des rayons X pour effacer les mémoires des smartphones, à travers le projet Repex. Le challenge ? Trouver le bon compromis entre un effacement complet et la préservation des autres composants, alors même que tous sont très imbriqués dans l’appareil.

Cette imbrication est au cœur des travaux de l’alliance Scarce, entre le CEA et l’université NTU de Singapour. Démarré en 2018 pour cinq ans, ce partenariat a été reconduit et vise à améliorer le recyclage des panneaux photovoltaïques, des batteries lithium et des circuits imprimés. « Un circuit contient entre 60 et 70 métaux critiques. En moyenne, les filières en recyclent 8, chiffre Jean-Christophe Gabriel, codirecteur de l’alliance. C’est une aberration : à la fabrication, on a fourni beaucoup d’efforts pour purifier ces matériaux et construire ces circuits et à la fin, on jette presque tout. » Le projet porté par Scarce mise sur un démontage pour récupérer les différents composants, puis un tri optimisé, grâce à une reconnaissance par IA et rayons X. En bout de chaîne, chaque panier de composants est homogène et peut contenir jusqu’à 10 % de métaux critiques. De quoi favoriser l’intérêt économique d’un recyclage !

Proposer des solutions à toutes les étapes, d’une fabrication économe en ressources jusqu’au recyclage, c’est là aussi une mission du CEA.