News | Press release

CEA-Leti Announces Collaboration with Intel to Advance Chip Design Through Cutting-Edge 3D Packaging Technologies

(c) CEA-Leti

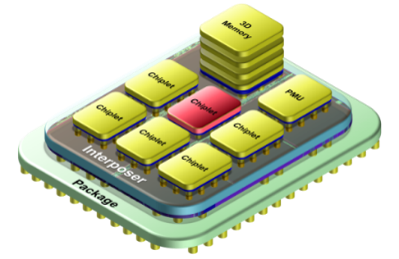

(c) CEA-Leti

Published on 27 October 2020

Body text

CEA-Leti Announces Collaboration with Intel to Advance Chip Design Through Cutting-Edge 3D Packaging Technologies

What's new: CEA-Leti today announced a new collaboration with Intel on advanced 3D and packaging technologies for processors to advance chip design. The research will focus on assembly of smaller chiplets, optimizing interconnection technologies between the different elements of microprocessors, and on new bonding and stacking technologies for3D ICs, especially for making high performance computing (HPC) applications.

Why it matters: 3D technology, which stacks chips vertically in a device, not only optimizes the power of the chip with advanced packaging interconnects between components, but it also allows the creation of heterogeneous integration of chiplets. That ultimately allows fabrication of more efficient, thinner and lighter microprocessors. In addition, by implementing multiple heterogeneous solutions in a single package, chip companies benefit from considerable flexibility, such as mixing and matching different technology blocks with different IP and integrating memory and input / output technologies within the same component. This enables chip makers to continue to innovate and adapt to the needs of their customers and partners.

In 2019, Intel introduced a 3D-stacking technology, Foveros, that adapted these design features. This advanced-packaging technology, launched in Intel® Core™ Processors with Intel Hybrid Technology (codenamed Lakefield) comes in a small physical package for significantly reduced board size to offer an optimal balance between performance and energy efficiency.

In 2019, Intel introduced a 3D-stacking technology, Foveros, that adapted these design features. This advanced-packaging technology, launched in Intel® Core™ Processors with Intel Hybrid Technology (codenamed Lakefield) comes in a small physical package for significantly reduced board size to offer an optimal balance between performance and energy efficiency.

At June 2020's IEEE Electronic Components and Technology Conference, CEA-Leti received the best paper award for its work, carried out at IRT Nanoelec on silicon active interposer as a promising solution towards 3D heterogeneous integration.These results pave the way to future high efficiency systems for high performance computing.

Top page